# Non-Contact EEG Active Multielectrode Hardware Design

by Scheina Gonzalez Supervised by Professor David Powers School of Computer Science, Engineering, and Mathematics Faculty of Science and Engineering Flinders University This thesis is submitted for the degree of Master of Engineering (Biomedical) 22 May 2017

## DECLARATION

I certify that this thesis does not incorporate without acknowledgement any material previously submitted for a degree or diploma in any university; and that to the best of my knowledge and belief it does not contain any material previously published or written by another person except where due reference is made in the text.

KIPE GONPORTEZ D.

Scheina Gonzalez Date: 03/01/2018

# ACKNOWLEDGEMENTS

I would like to express my deep gratitude to all those who helped and supported me throughout this process and made this submission possible.

Firstly, I would like to thank my supervisor Professor David Powers for the opportunity to engage in this work with him, for his continuous support, motivation, time, and valuable advice. Thank you for your patience and dedication.

I would also like to thank Craig Peacock, Damian Kleiss and Fiona Cramer from the CSEM Engineering Service for their continued technical advice.

Editor, Alexander Gosewinckel, provided copyediting and proofreading services, according to the conditions laid out in the university-endorsed national guidelines 'The editing of research theses by professional editors'.

# Abstract

The electroencephalogram (EEG) is a widely employed method of measuring electrical activity of the brain for medical diagnosis and research. This electrical activity is generated a few centimetres below the electrode employed in the measurement. As a result of this, the cortical current must travel across different resistive levels causing a blurring effect of brain activity at the scalp. Furthermore, spatial smearing occurs from the necessary use of a reference electrode to measure the potential difference. An important method utilised to improve EEG spatial resolution is the surface Laplacian. There are various methods that have been used to improve EEG poor spatial resolution in the past. The tripolar concentric ring electrode (TCRE), is an electrode that was developed to improve the surface Laplacian and consequently improve poor spatial resolution. The first part of this thesis involves the design and assembly of a non-contact segmented capacitive TCRE. This new design seeks to improve not only the surface Laplacian and the noise ratio also seeks to increase the communication rate of the EEG and detect and distinguishing of motor and sensory input from the body. For verification a filter stage was designed and tested the reliability of the signal acquired. Some problems occurred during the experiment showing that there was an analogue floating input that affected the signal acquisition. The second stage of the thesis was dedicated to designing the digitalisation, control, and communication system of a BCI. To achieve this, the circuits and PCBs of this stage including AFE and BLE were designed. It was not possible to test this design as time constraints of the project did not allow for its assembly.

# TABLE OF CONTENTS

| AB  | STRAC   |                |                                             |    |

|-----|---------|----------------|---------------------------------------------|----|

| LIS | T OF TA | BLES           |                                             |    |

| 115 | T OF FI | SURES          |                                             | 2  |

|     |         |                |                                             |    |

| LIS | T OF A  | BREVIATION     | S AND SYMBOLS                               |    |

| 1.  | INTF    | ODUCTION       |                                             | 5  |

| 2.  | PRO     | ECT BACKGR     | OUND                                        | 6  |

|     | 2.1.    | EEG            |                                             | 6  |

|     | 2.2.    | SIGNAL ACQUIS  | ITION AND TYPE OF ELECTRODES                |    |

|     | 2.3.    | PREVIOUS LITER | RATURE                                      |    |

|     | 2.3.1   | . Surface      | Laplacian in EEG detection                  |    |

|     | 2.3.2   | . Capacit      | ive tilt non-contact electrode design       |    |

|     | 2.3.3   | . Active n     | non-contact electrode design                |    |

| 3.  | PRO     | ECT SCOPE      |                                             | 23 |

|     | 3.1.    |                |                                             | 23 |

|     | 3.2.    |                | · · · · · · · · · · · · · · · · · · ·       |    |

|     | 3.2.1   |                | ıre and Deliverables                        |    |

| 4.  | MET     |                |                                             |    |

|     |         |                |                                             |    |

| 5.  | DESI    | GN OVERVIEV    | N                                           | 25 |

| 6.  | NON     | -CONTACT EL    | ECTRODE                                     | 26 |

|     | 6.1.    | MATERIAL USE   | IN ELECTRODES AND THEIR CHEMISTRY           |    |

|     | 6.2.    | ELECTRODE DES  | 5IGN                                        | 27 |

|     | 6.3.    | SHAPE DESIGN.  |                                             | 27 |

|     | 6.4.    | CAPACITANCE    |                                             |    |

|     | 6.5.    | AMPLIFICATION  | (Readout Circuit)                           |    |

|     | 6.5.1   | . Circuit l    | Design                                      |    |

|     | 6.5.2   | . Followe      | er Stage Analysis                           |    |

|     | 6.5.3   | . Non-Inv      | verter Stage Analysis                       |    |

| 7.  | ANA     | LOGUE FRON     | T ENDS (AFES) FOR BIOPOTENTIAL MEASUREMENTS |    |

|     | 7.1.    | AFEs CONCEPT   |                                             |    |

|     | 7.2.    | AFE SPECIFICAT | ION REQUIREMENT                             |    |

|     | 7.3.    | TYPES OF ANAL  | OGUE TO DIGITAL CONVERTERS (ADC)            |    |

|     | 7.3.1   | . Delta Si     | igma (ΔΣ)                                   |    |

| 7.3.             | 2. SARs                                                           |    |

|------------------|-------------------------------------------------------------------|----|

| 7.4.             | АГЕ Сноісе                                                        |    |

| 7.4.             | 1. ADS129X                                                        |    |

| 8. MIC           | RO CONTROL UNIT (MCU) AND BLUETOOTH LOW ENERGY (BLE)              |    |

|                  |                                                                   |    |

| 8.1.             | MCU CONCEPT                                                       |    |

| 8.2.             | BLE                                                               |    |

| 8.3.             | MCU/BLE                                                           |    |

| 8.3.             |                                                                   |    |

| -                | .3.1.1. DA14680<br>2. Atmel (Arduino)                             |    |

| <i>8.3.</i><br>° | <ol> <li>Atmer (Arduno)</li></ol>                                 |    |

| ہ<br>8.4.        | MCU Comparison                                                    |    |

|                  |                                                                   |    |

| 9. PRII          | NTED CIRCUIT BOARDS (PCBS) LAYOUT DESIGN                          |    |

| 9.1.             | Software Tool                                                     | 42 |

| 9.2.             | EEG SENSOR                                                        |    |

| 9.2.             | 1. Consideration of the layout                                    | 42 |

| 9                | .2.1.1. Shielding                                                 | 42 |

| 9                | .2.1.2. Grounding                                                 |    |

| 9.3.             | Analogue Front End                                                | 43 |

| 9.3.             | 1. Layout                                                         | 44 |

| 9.4.             | BLE LAYOUT DESIGN                                                 |    |

| 9.4.             | 1. Layout                                                         | 46 |

| 10. S            | OFTWARE DEVELOPED                                                 | 48 |

| 10.1.            | BLE FIRMWARE                                                      | 48 |

| 10.1.            | BLE CODE DESIGN                                                   | _  |

| 10.2.            | Electrode Testing code                                            | -  |

|                  |                                                                   |    |

| 11. S            | AFETY                                                             | 51 |

| 12. N            | IEASUREMENT SETUP                                                 | 52 |

| 12.1.            | Setup                                                             |    |

| 12.2.            | CAPACITANCE MEASUREMENT                                           |    |

| 12.3.            | FILTER AND AMPLIFICATION CIRCUIT                                  |    |

| 12.4.            | Electrode test                                                    |    |

|                  |                                                                   |    |

| 13. R            | ESULTS AND DISCUSSION                                             | 57 |

| 13.1.            | Electrode design                                                  | 57 |

| 13.2.            | Readout circuit                                                   |    |

| 13.3.            | BAND PASS FILTER AND COMMON MODE CIRCUIT FOR THE TESTING PURPOSE  | 59 |

| Scheina          | a Gonzalez: Non-Contact EEG active Multielectrode Hardware Design | 5  |

| 13.4.            | PROBLEM CAUSED BY THE POWER LINE      | 59 |

|------------------|---------------------------------------|----|

| 13.5.            | AFE AND BLE CIRCUIT AND PCB DESIGN    | 60 |

| 14. (            | CONCLUSION                            | 63 |

| 15. I            | FUTURE WORK AND RECOMMENDATIONS       | 64 |

| REFEREN          | ICES                                  | 65 |

| APPEND           | IX A: GANTT PROJECT PLANER            |    |

|                  | IX B: COMPONENTS LIST                 |    |

|                  | IX C: ELECTRODE SCHEMATIC             |    |

| APPEND           | IX D: READOUT SCHEMATIC               | 73 |

| D.1. G           | LOBAL IMPLEMENTATION                  | 73 |

| D.2. E           | LECTRODE AMPLIFICATION CIRCUIT        | 74 |

| D.3. C           | ENTER ELECTRODE AMPLIFICATION CIRCUIT | 75 |

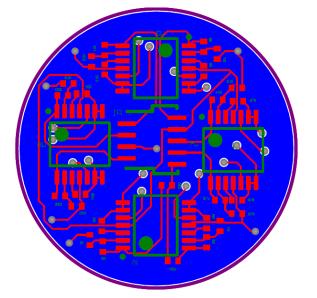

| APPEND           | IX E: LAYOUT SENSOR                   | 76 |

| E.1. R           | EADOUT PCB LAYOUT                     |    |

| E. <b>2</b> . El | ECTRODE PCB LAYOUT                    | 77 |

| E.3.3[           | D Electrode PCB Print                 |    |

| E.4. R           | eadout 3D Layout                      | 79 |

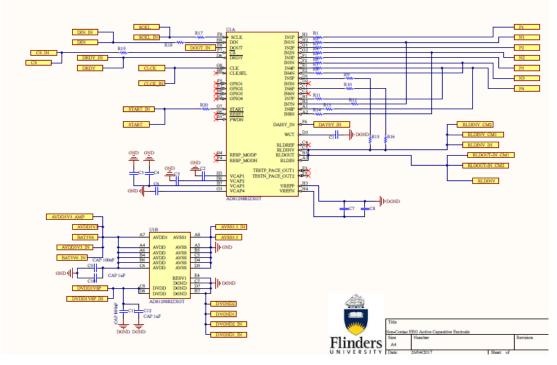

| APPEND           | IX F: AFE SCHEMATIC                   | 80 |

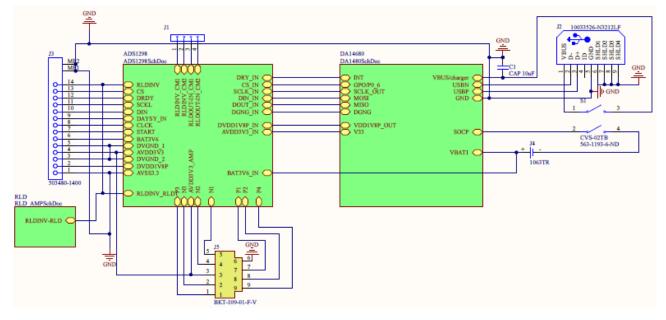

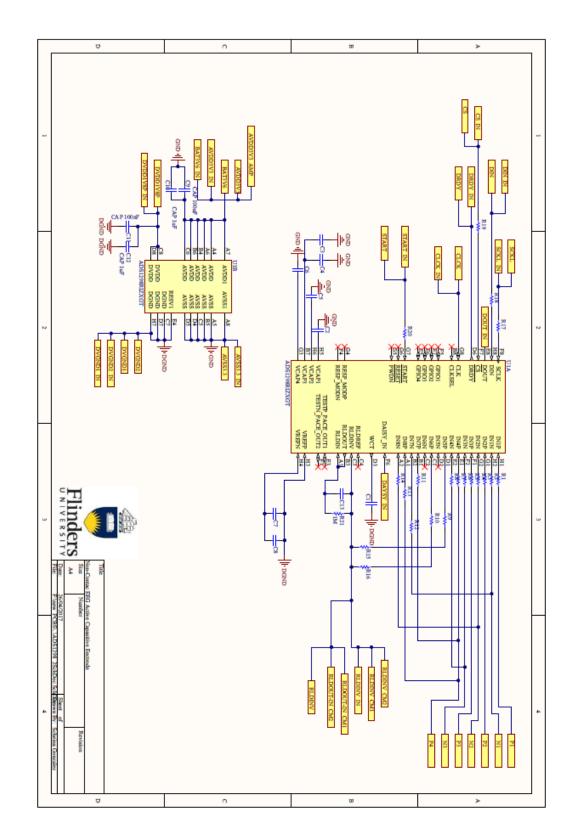

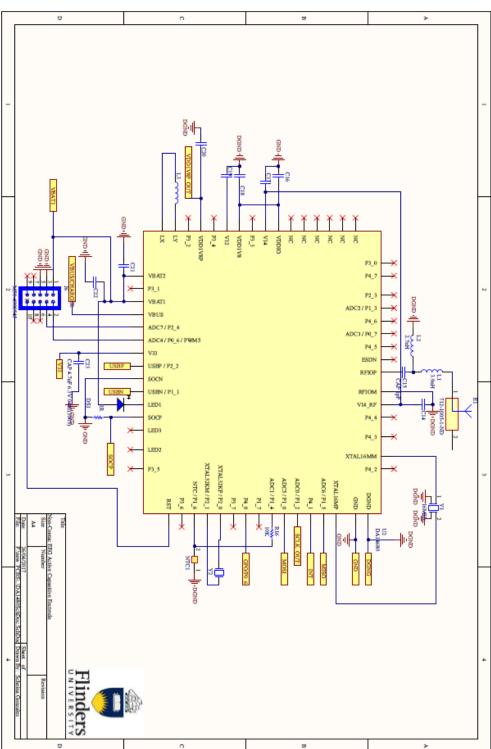

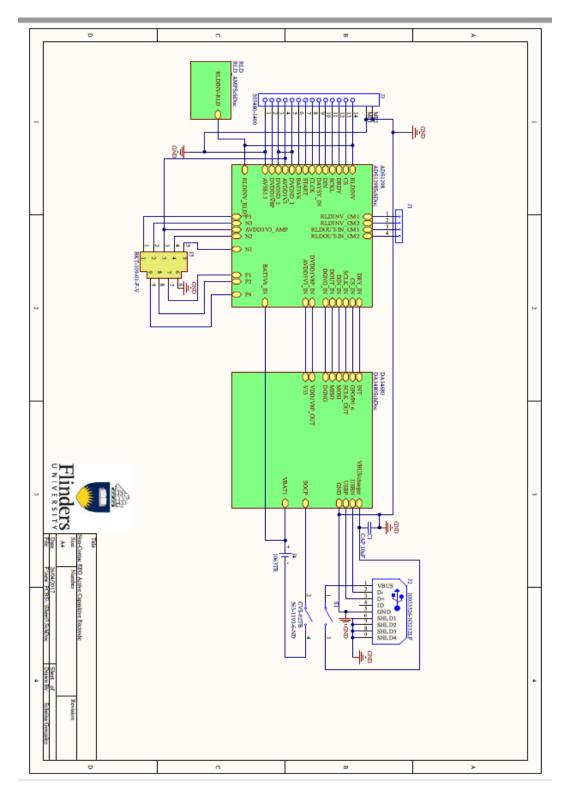

| F.1. AI          | DS1298 Schematic circuit              | 80 |

| F.2. Di          | IGITALIZATION SCHEMATIC CIRCUIT       | 81 |

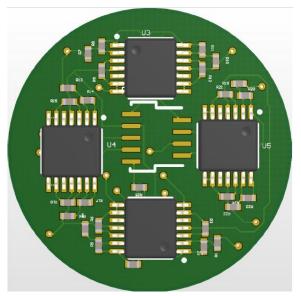

| APPEND           | IX G: AFE PCB LAYOUT                  | 82 |

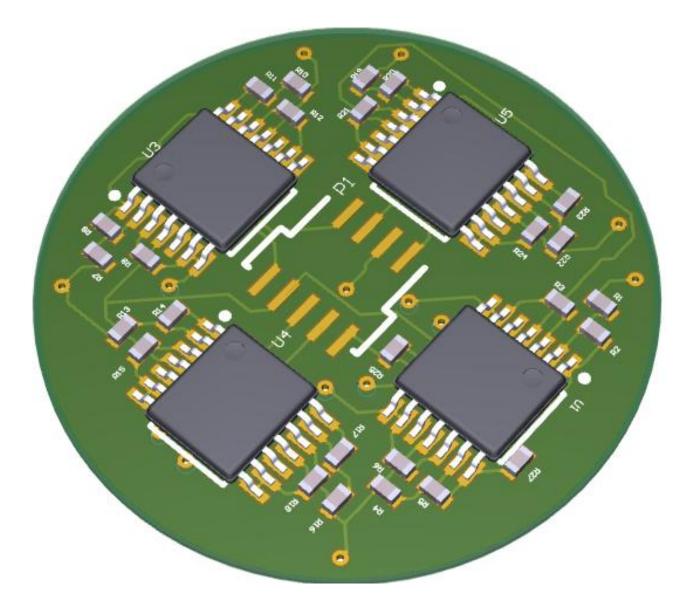

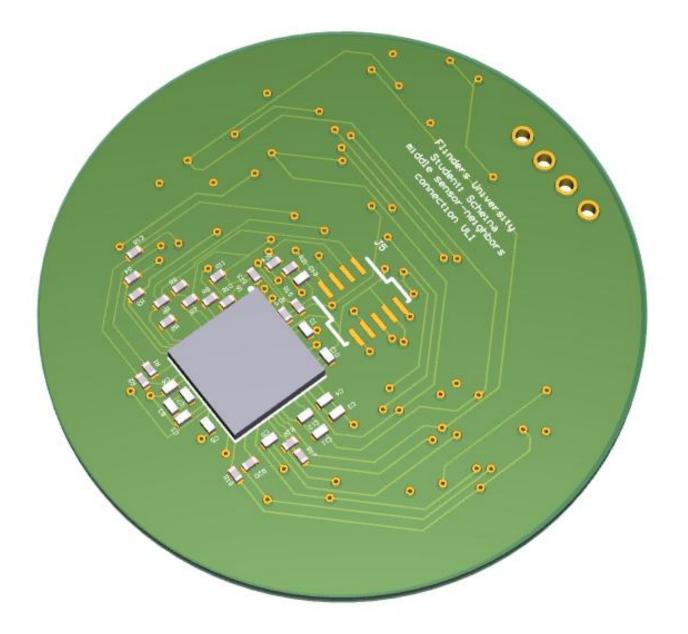

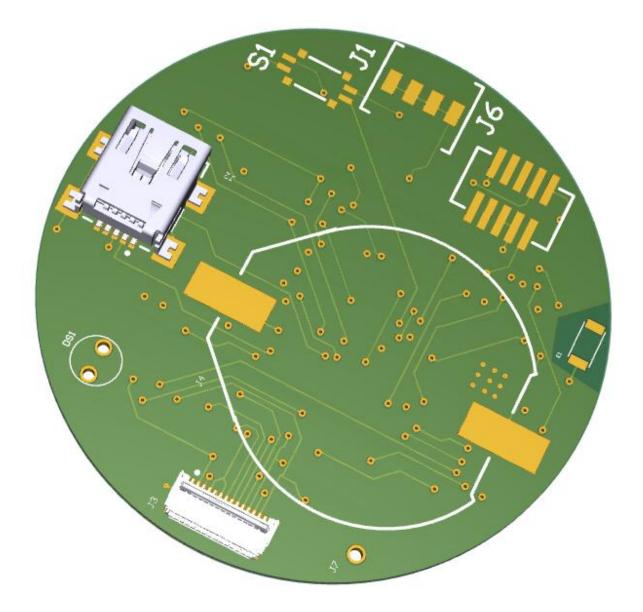

| G.1.3            | D TOP PCB PRINT                       | 82 |

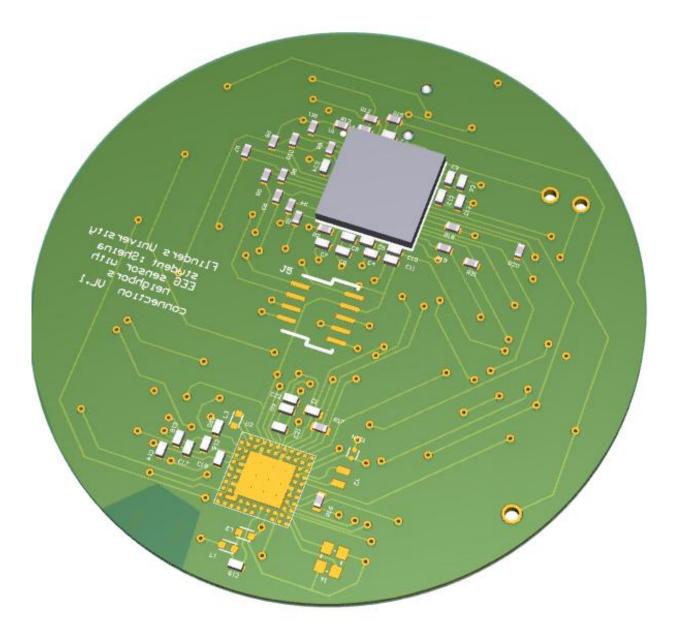

| G.2.3            | D BOTTOM PCB PRINT                    | 83 |

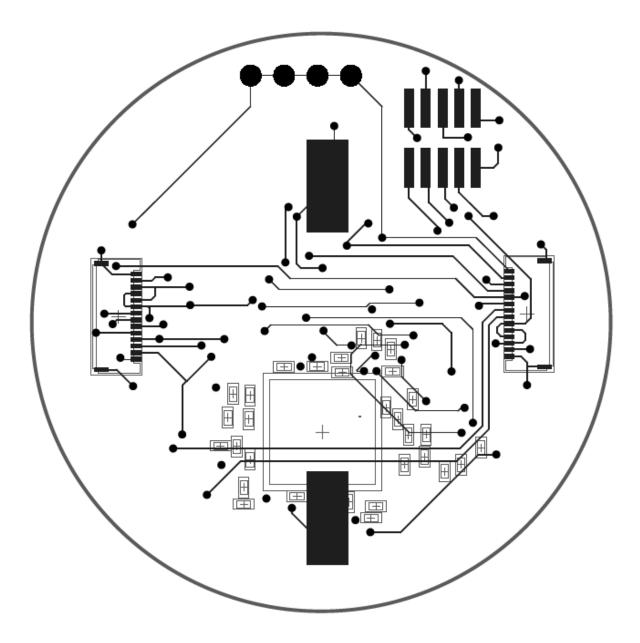

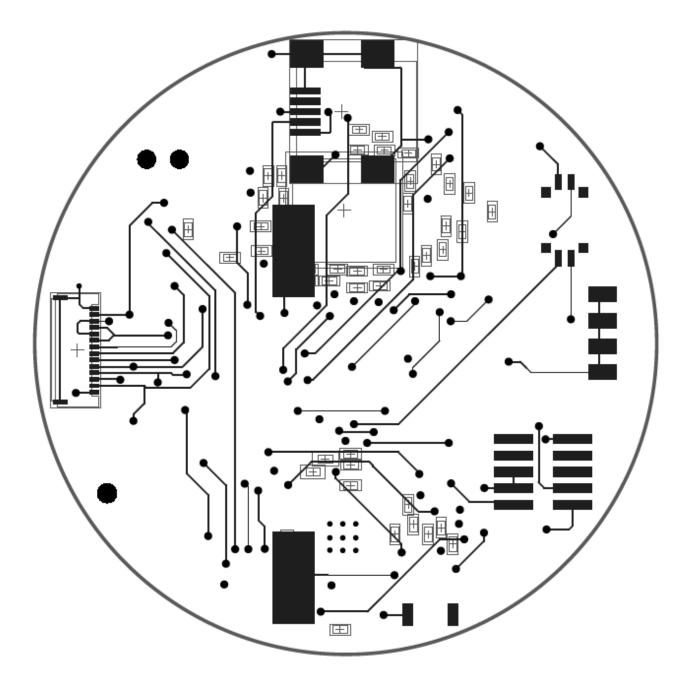

| G.3. Fi          | NAL ARTWORK TOP LAYER PRINT           |    |

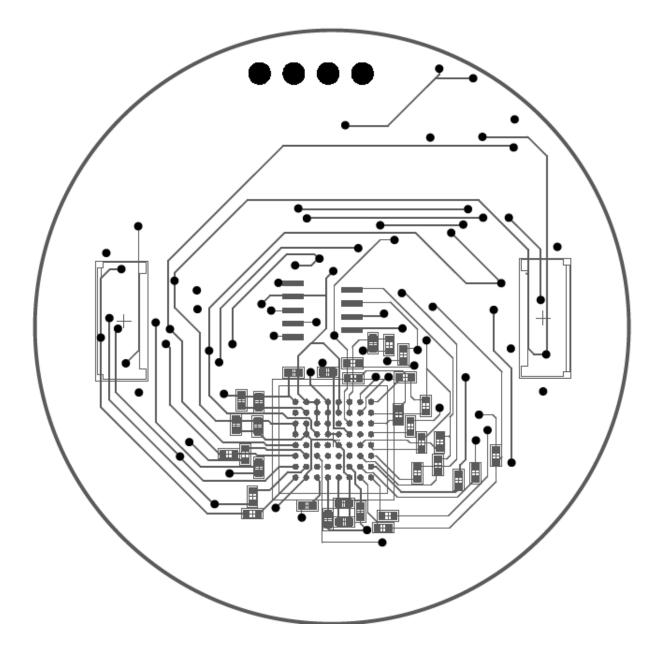

| G.4. Fi          | inal Artwork Bottom Layer Print       | 85 |

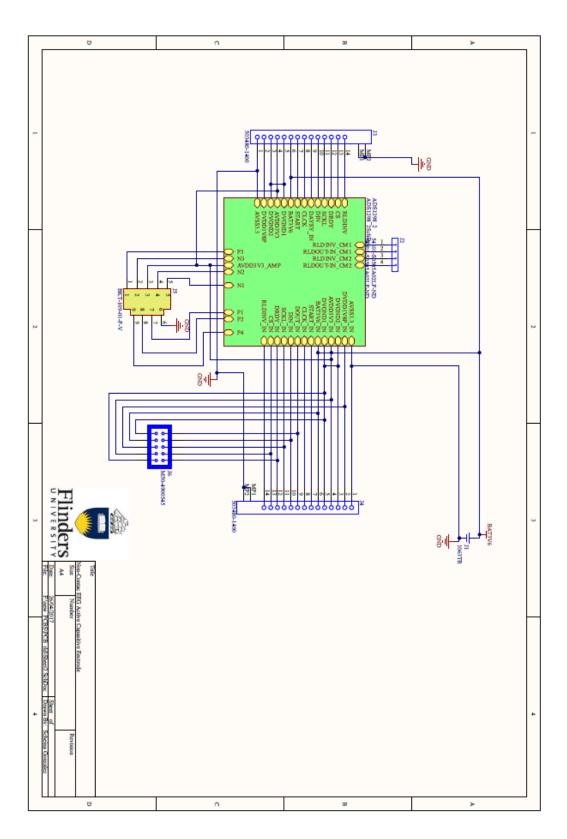

| APPEND           | IX H: BLE SCHEMATIC                   | 86 |

| H.1. D           | A14680 Schematic Circuit              | 86 |

| H.2. C           | OMMUNICATION PCB SCHEMATIC CIRCUIT    | 87 |

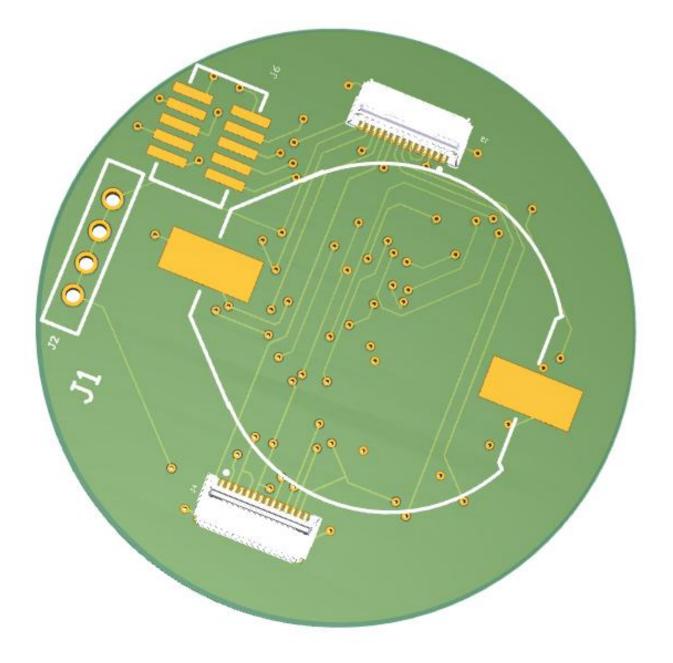

| APPEND           | IX I: CONTROL AND COMMUNICATION PCB   | 88 |

| I.1. 3D          | ) TOP PCB PRINT                       |    |

| 1.2. 3D          | BOTTOM PCB PRINT                      |    |

| 1.3. Fin         | JAL ARTWORK TOP LAYER                 | 90 |

| 1.4. Fin         | ial Artwork Bottom Layer              | 91 |

| APPENDIX J: RISK ASSESSMENT FORMAT | 92 |

|------------------------------------|----|

| APPENDIX K: CODE                   | 93 |

| K.1. FRI BAND PASS FILTER          | 93 |

| K.2. BLUETOOTH TESTING             | 93 |

| K2.1. MATLAB CODE                  | 93 |

| K2.2. Arduino code                 | 95 |

| K2.2.1. ADS1298.h                  | 95 |

| K2.2.2 Main code                   |    |

| K.2.2.3. SPI communication         |    |

| K.3 Smart snippets                 |    |

| K.3.1 ADS.c                        |    |

| K3.2 Main.c                        |    |

| K.3.3 system configuration         |    |

# List of Tables

| TABLE 1 - MAIN TYPES OF EEG ELECTRODES [14, 16]                                                | 8  |

|------------------------------------------------------------------------------------------------|----|

| TABLE 2 - ELECTRODE PERFORMANCE IS EMPLOYING A DIFFERENT MATERIAL FOR COATING [32]             | 27 |

| TABLE 3 - DIMENSION, RING SEPARATION, AND CAPACITANCE CALCULATION OF THE ELECTRODE (REFERENCE) | 29 |

| TABLE 4 - PARAMETRIC OF ADS1298 AND ADS1299 [43, 42]                                           | 35 |

| TABLE 5 - MCU COMPARISON                                                                       | 41 |

| TABLE 6 - OPCODE COMMAND DEFINITIONS [43]                                                      | 50 |

| TABLE 8 - CAPACITANCE MEASUREMENT                                                              | 54 |

| TABLE 9 - BUTTERWORTH FILTER SPECIFICATIONS                                                    | 55 |

# List of Figures

| FIGURE 1 - EXTRACELLULAR TRACES- EEG IMAGE RECORDING [1]7                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------|

| Figure 2 - Amplitude and Frequency of the biopotential signals [14]                                                         |

| FIGURE 3 - TYPES OF EEG BIOPOTENTIAL ELECTRODES: (A) WET ELECTRODE, (B) DRY ELECTRODE AND (C) NON-CONTACT ELECTRODE [17]. 9 |

| FIGURE 4 - REGULAR PLANE SQUARED GRID WITH INTERPOINT DISTANCE EQUAL TO R USED BY MAKEYEV AND BESIO [2]10                   |

| Figure 5 - Parameter of the segmented coplanar sensor findings [20]11                                                       |

| Figure 6 - Electrode design (Author's own)                                                                                  |

| FIGURE 7 - MICRO POWER NON-CONTACT EEG ELECTRODE WITH ACTIVE COMMON-MODE NOISE SUPPRESSION AND CAPACITIVE INPUT             |

| CANCELLATION [25]                                                                                                           |

| Figure 8 - EEC signal [25]                                                                                                  |

| Figure 9 - Schematic of Non-Contact electrode design [26]14                                                                 |

| Figure 10 - EEG data from the 2010 design [26]14                                                                            |

| Figure 11 - Second EEG Schematic deign presented in 2010 [27]                                                               |

| FIGURE 12 - DATA FROM THE ACQUIRED FROM THE ECG EXPERIMENT (RED TRACE OBTAINED USING RED DOT AND THE BLACK SIGNAL OBTAINED  |

| BY USING NON-CONTACT ELECTRODE) [27]                                                                                        |

| Figure 13 - Schematic of the Non-contact sensor front end [28]                                                              |

| FIGURE 14 - SAMPLES OBTAINED BY USING STANDARD AG/AGCL (BLUE SIGNAL) AND NON-CONTACT FRONT END (RED SIGNAL) [28]            |

| FIGURE 15 - CONCEPT AND IMPLANTATION OF USED IN THE COMPACTION DRY EEG ELECTRODE [29]                                       |

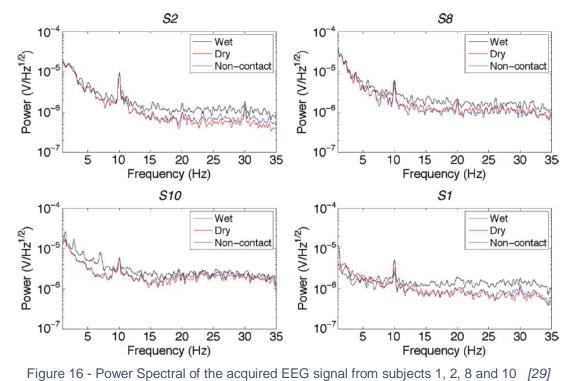

| FIGURE 16 - POWER SPECTRAL OF THE ACQUIRED EEG SIGNAL [29]                                                                  |

| Figure 17 - Non-contact Schematic and prototype [30]20                                                                      |

| Figure 18 - Adaptive mechanical design [30]20                                                                               |

| FIGURE 19 - EEG SIGNAL AND SPECTRA DETECTED BY THE NON-CONTACT SENSOR FOR THE SSVEP EXPERIMENT [30]                         |

| FIGURE 20 - MEASUREMENT OF EEG UNDER A MOTION ARTEFACT [30]22                                                               |

| FIGURE 21 - BLOCK DIAGRAM OF NON-CONTACT EEG ACTIVE MULTIELECTRODE HARDWARE DESIGN (AUTHOR'S OWN)                           |

| FIGURE 22 - CROSS-SECTION OF THE CAPACITIVE ELECTRODE PCB (AUTHOR'S OWN)                                                    |

| Figure 23 - Schematic of the capacitive electrode [34]                                                                      |

| FIGURE 24 SCHEMATIC CIRCUIT OF THE READOUT AMPLIFICATION CIRCUIT (AUTHOR'S OWN)                                             |

| Figure 25 Buffer stage of the readout circuit (Author's own)                                                                |

| Figure 26 - Gain stage of the read-out Circuit (Author's own)                                                               |

| FIGURE 27- FUNCTIONAL DIAGRAM OF THE ADS1298 AND 1299 [42, 41]                                                              |

| Figure 28 - DA14680 Block diagram [46]                                                                                      |

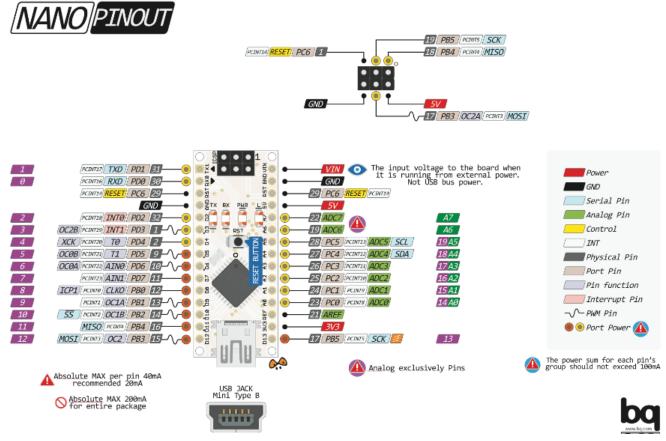

| Figure 29 Arduino Nano Pinout [47]40                                                                                        |

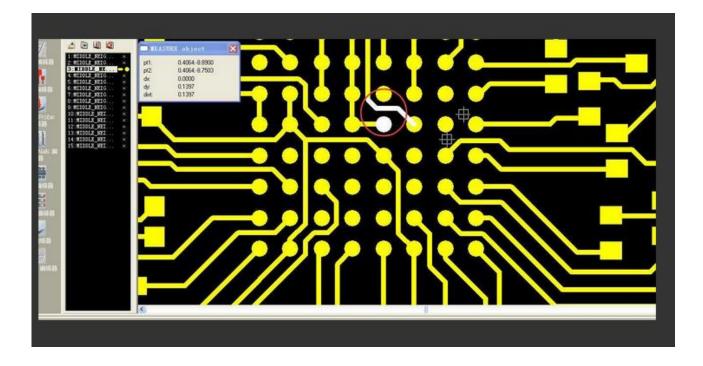

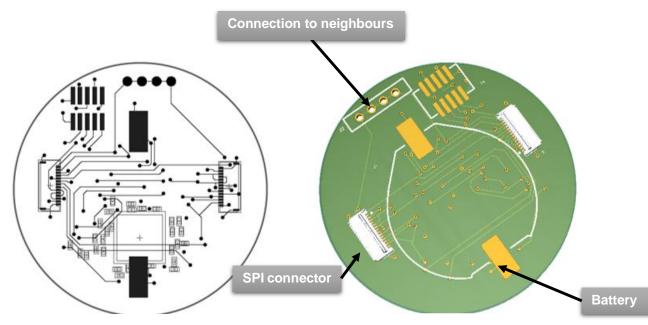

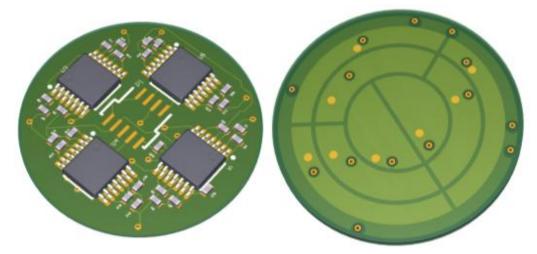

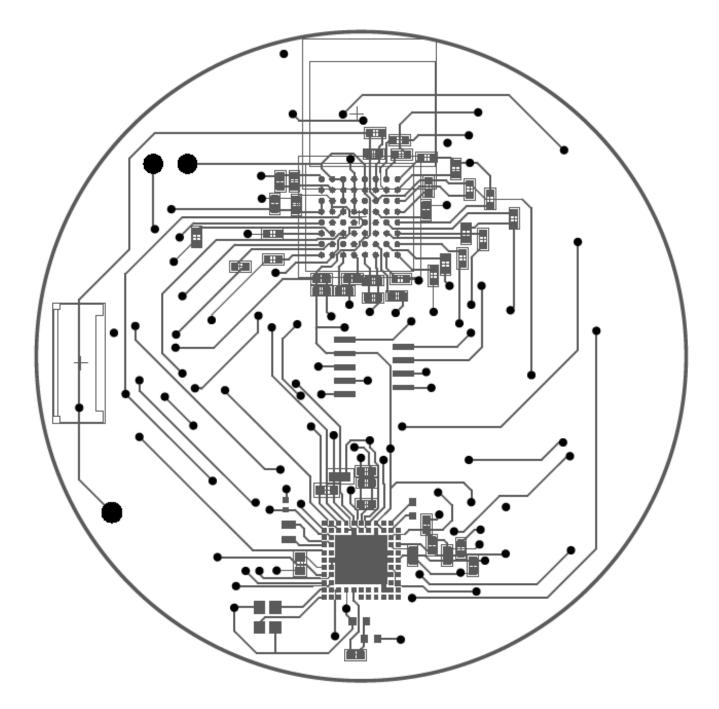

| FIGURE 30 - 2D LAYOUT OF THE FINAL READOUT PCB DESIGN FIGURE 31 - 3D PCB LAYOUT (AUTHOR'S OWN)43                            |

| Figure 32 - ADS1298 schematic circuit (Author's own)                                                                        |

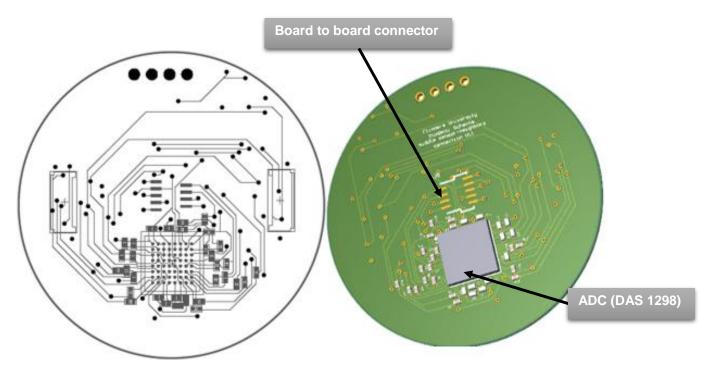

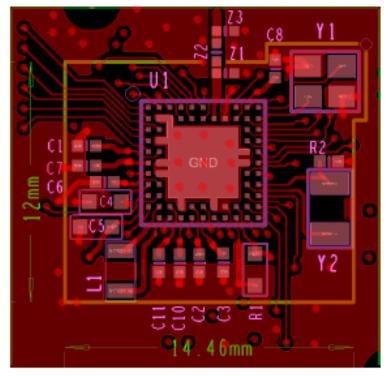

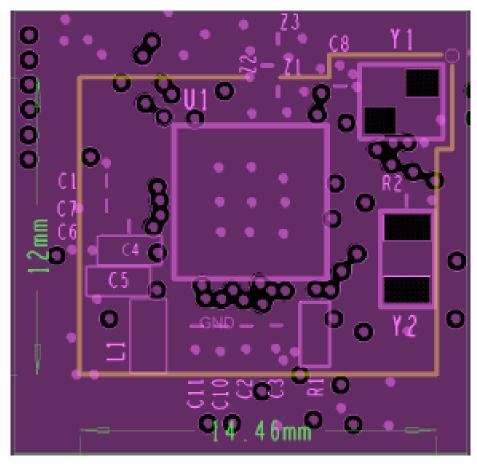

| FIGURE 33 - TOP LAYER OF THE ANALOGUE TO DIGITAL CONVERTER PCB (AUTHOR'S OWN)                                               |

| FIGURE 34 - BOTTOM LAYER OF THE ANALOGUE DIGITAL CONVERTER PCB (AUTHOR'S OWN)45                                             |

| Figure 35 - BLE schematic circuit (Author's own)46                                                                          |

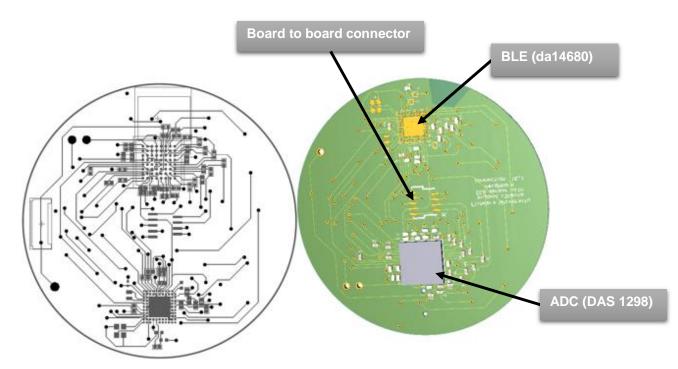

| FIGURE 36 BOTTOM LAYER OF THE BLUETOOTH LOW ENERGY MCU AND ANALOGUE TO DIGITAL CONVERTER PCB (AUTHOR'S OWN)                 |

| FIGURE 37 - TOP LAYER OF THE BLUETOOTH LOW ENERGY MCU AND ANALOGUE TO DIGITAL CONVERTER PCB (AUTHOR'S OWN) | 47 |

|------------------------------------------------------------------------------------------------------------|----|

| Figure 38 ADS1298 Power up Block diagram [42]                                                              | 49 |

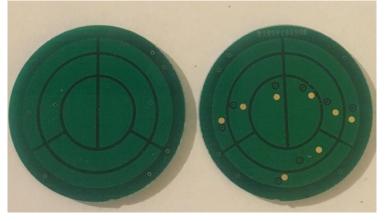

| Figure 39 - Segmented TCRE prototype (Author's own)                                                        | 52 |

| Figure 40 - Sensor and dummy electrode connected back to back (Author's own)                               | 53 |

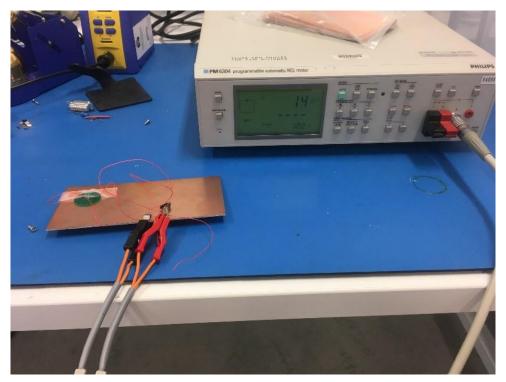

| Figure 41 - Capacitance measurement (Author's own)                                                         | 54 |

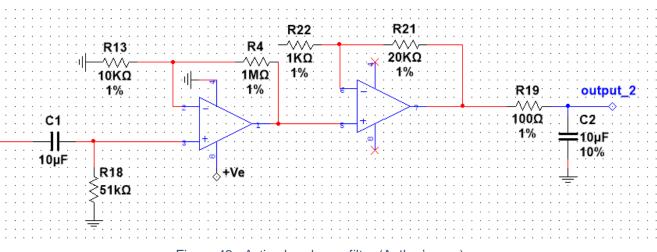

| Figure 42 - Active band pass filter (Author's own)                                                         | 56 |

| Figure 43 - Resulting electrode design (Author's own)                                                      | 57 |

| Figure 44 - PCB of the readout circuit and the electrode (Author's own)                                    | 58 |

| Figure 45 - Common mode Circuit (Author's own)                                                             | 59 |

| Figure 46 distorted and attenuated signals results                                                         | 60 |

|                                                                                                            |    |

# List of Abbreviations and Symbols

### Abbreviations

| ADC     | Analogue to Digital Converter               |

|---------|---------------------------------------------|

| Ag/Agcl | Silver / Silver Chloride                    |

| AFE     | Analogue Front Ends                         |

| BCI     | Brain Computer Interface                    |

| BLE     | Bluetooth Low Energy                        |

| CC/CV   | Constant Current / Constant Voltage         |

| CMOS    | Complementary Metal Oxide semiconductor     |

| CMRR    | Common mode rejection ration                |

| CREs    | Concentric ring electrode                   |

| DC      | Direct Current                              |

| DSP     | Digital Signal Processors                   |

| DRL     | Driven right Leg                            |

| ECG     | Electro cardiograph                         |

| EEG     | Electro encephalograph                      |

| IDE     | Integrated developed environment (Arduino)  |

| I/O     | Input/ output                               |

| I2C     | Inter integrated                            |

| MCU     | Micro Control Unit                          |

| MISO    | Master input Salve output                   |

| MOSI    | Master output slave Input                   |

| OTP     | Open Telecommunication Platform             |

| OP-AMP  | Operational Amplifier                       |

| PCB     | Printed Circuit Board                       |

| SAR     | Successive Approximation                    |

| SC      | Chip Selection                              |

| SCLK    | Serial Clock                                |

| SPE     | Signal Processing Element                   |

| SSVEP   | Steady State Visual Evoked Potential        |

| SS      | Slave selection                             |

| SPI     | Serial Peripheral Interface                 |

| TCRE    | Tripolar Concentric Ring Electrode          |

| TGA     | Therapeutic Goods Administration            |

| UART    | Universal Asynchronous receiver/Transmitted |

| ΔΣ      | Delta-sigma                                 |

| SYMBOL  |                                             |

| OZ      | EEG POSITION                                |

## 1. Introduction

An Electroencephalogram (EEG) is a test which measures the electrical activity within a brain [1]. Its method is non-invasive and its output highly valuable in brain and behaviour research. Therefore EEG has become a pillar of hospital diagnosis and pre-surgical planning [2, 3].Despite its advantages, this method is hampered by low spatial resolution, i.e. a selectivity low signal-to-noise ratio. The low spatial resolution is a result of the blurring effects of the volume conductor with the plate or disc electrodes [2].

One method to reduce the blurring effect and improve the spatial resolution is surface Laplacian differentiation, which is the second spatial derivative of the potential distribution on the scalp's surface [2]. The surface Laplacian can aid Brain-Computer Interface (BCI) research with at least in two functions; firstly by working as a spatial filter and reducing spatial noise, and secondly by limiting the potential sources of the signal [4]. In order to minimise the low spatial frequency and enhance the spatial selectivity in EEG, one may also employ non-invasive concentric ring electrodes (CREs) [2]. Moreover, it has been shown that a tripolar CRE (TCRE) can estimate the surface Laplacian utilising the nine-point method, an extension of the five-point method [2]. A TCRE possesses better spatial selectivity and signal-to-noise ratio than traditional disc electrodes [2].

The BCI is a system that can be controlled by a subject by using brain signals, which can be used to help patients with disabilities [5, 6]. EEG is one of the most commonly employed signals in BCI application since it has a good temporal resolution, can be measured non-invasively and it is relatively inexpensive [5, 6]. There are numerous types of BCI systems which are based on different paradigms and methods of EEG collection, one example being the Steady State Visual Evoked Potential (SSVEP) [5, 6]. The most commonly used BCI systems are based on visual evoked potentials (VEPs) which are currently the fastest method to set non-invasive BCI control [5, 6] However, SSVEP is normally for picking up frequencies, while other potentials for spikes, without depending on spatial localization.

The work presented in this paper has attempted to design capacitive tripolar segmented active electrodes that can overcome the aforementioned disadvantages of EEG, specifically spatial resolution and low signal-to-noise ratios. This project also aims to design a system capable of collecting and transmitting the EEG signal to a computer via Bluetooth for the purpose of visualisation. The new design seeks to streamline the detection and localisation of motor and sensory signals down to a few mm; a requirement to distinguish finger movement in the sensory motor cortex. Currently the detection of fingers in the sensory motor cortex is only be distinguishable by employing invasive electrodes.

## 2. PROJECT BACKGROUND

#### 2.1. EEG

The Electroencephalogram (EEG) is the recording of the neural electrical activity within brain structure from the scalp surface after being collected by a metal electrode. The EEG record is a spatiotemporal method, and it is a smoothed version of the local field potential (LFP) [7]. The results are presented in a voltage versus time graph where the y-axis is voltage, and the X axis is time as is shown in [1, Fig. 1]. The EEG is an entirely non-invasive method that can be conducted on any patient without having any risk or major discomfort and records information processed by neurons by means of electrical signals [8, 9]. In the generation of the EEG, the large cortical pyramidal neurons located in the deep cortical layer play an important role because of the neuron's orientation with their apical dendrites, being perpendicular to the cortical surface [9].

The current which is contributed to by the active cellular processes in a specific volume of the brain tissues is superimposed at a specific area in the extracellular medium, and this generates a potential in respect to a reference potential, measured in volts (V) [7]. This potential difference generates an electrical field which is a vector whose amplitude is measured in volts per distance, and it is defined as the negative spatial gradient of  $V_e$ [7].  $V_e$  historically has been assigned to the EEG when this is recorded from the scalp [7].

The EEG is one of the oldest and most extensively employed methods for brain electrical activity research. The first EEG recorder was developed by German neuropsychiatrist Hans Berger in 1924, however, his results were not published until 1929. This report presented a recorded of alpha rhythm and alpha blocking response of Hans Berger's son [8, 10]. EEG has since become one of the most significant contributions to clinical diagnosis and electrophysiology. In a practical medical scenario, an EEG can allow the determination of relevant clinical parameters such as the location and the classification of seizures [11, 12]. Thus, a strong correlation exists between the development of EEG and the classification and understanding of clinical diseases such as encephalopathy and epilepsy. Additionally, EEG is used for neurofeedback in order to induce long-term changes in the human corticomotor excitability by employing Brain Computer Interface (BCI), achieved by establishing a causal link between cortical activity and their function [13].

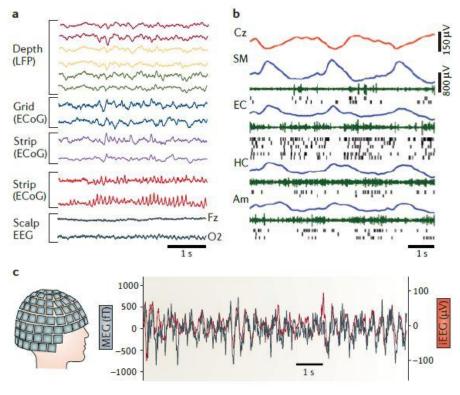

Figure 1 - Extracellular traces- EEG image recording [1]

#### 2.2. Signal Acquisition and type of electrodes

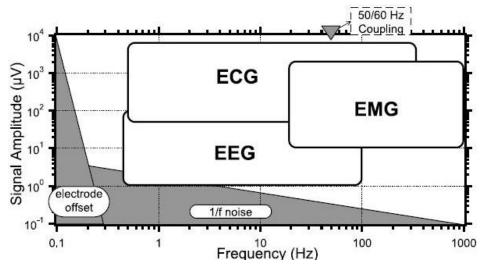

The EEG signal acquisition is conducted by placing electrodes on the scalp surface in order for the voltage of the electrodes and the reference to be measured [14]. [14, Fig.2] shows amplitude and the frequency of the biopotential signal, and as is evident, the maximum amplitude of an EEG signal is around 1mV, and the maximum frequency is approximately 100Hz [14]. In order to collect a clean EEG signal, it is necessary to reject or filter the correlating signal such as DC electrode offset voltage and the noise from the other biopotential signals [14]. Moreover, to obtain a signal at a working level, it is necessary to add amplification.

The EEG biopotential electrode is a transducer interface between the scalp and the circuit that converts an ion current to an electric current [14, 15]. The biopotential electrode performance principle is explained by an electrolyte interface [14, 15]. A chemical reaction occurs at the electrode-electrolyte interface to enable the current flow between the electrolyte which does not have free electrons and the electrode that does not have free cations [14, 15]. When the chemical reaction depends on the concentration of the cations, a charge gradient is formed at the electrode- electrolyte interface, which result in a potential difference between the interface called half-cell potentials [14, 15].

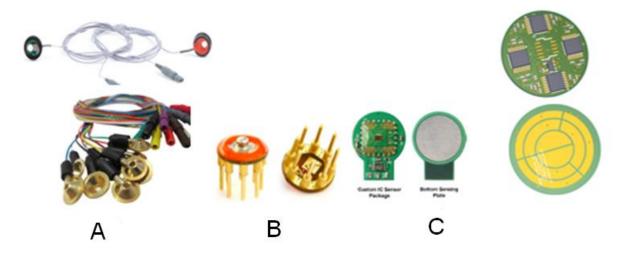

The EEG biopotential electrodes are classified as being either wet electrodes, dry electrodes, or non-contact electrodes. The most relevant characteristics of each type of electrode are summarised in [14, 16, Tab. 1]. A wet electrode is the most common type of electrode employed in biopotential measurement. This kind of electrode utilises conductive gel for the purpose of acting as an electrolyte

in order to create better contact between the electrode and the scalp [15, 14]. The advantage of wet electrodes is that they present low motion artefact and low impedance. Despite this, the time of preparation from the gel smearing and the removal of the gel is problematic [14, 15, 16].

| Electrode Type             | Advantage                                                                                                                                                                              | Disadvantage                                                                                                                                    |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Wet                        | <ul> <li>Close to non-polarise</li> <li>Low Motion artefact</li> <li>Common</li> </ul>                                                                                                 | <ul> <li>Require Conductive gel</li> <li>Require a long time for preparation</li> <li>Gel Smearing</li> <li>Unpractical gel remotion</li> </ul> |  |

| Dry                        | <ul> <li>conductive Gel is not required</li> <li>faster implementation</li> </ul>                                                                                                      | <ul> <li>it affected for Motion artefact</li> <li>require readout Circuit</li> <li>Highly polarisable</li> </ul>                                |  |

| Non-contact/<br>Capacitive | <ul> <li>conductive gel is not required</li> <li>easy implementation</li> <li>it does not required skin preparation</li> <li>it can be used for long term signal collection</li> </ul> | <ul> <li>high input impedance</li> <li>high affected for motion artefact</li> <li>required active readout circuit</li> </ul>                    |  |

Table 1 - Main types of EEG electrodes [14, 16]

Figure 2 - Amplitude and Frequency of the biopotential signals [14]

Dry electrodes do not need conductive gel to conduct and enhance the electrode-electrolyte connection [14, 15], therefore the main advantage compared to wet electrodes is the time of preparation. However due to its leaky capacitive characteristics, this type of electrode requires a high input impedance readout circuit which should be placed closer to the electrode [14, 15].

Non-contact electrodes are considered to be a pure capacitive electrode [14, 15]. The primary advantages of this type of electrode are that it can remotely sense the EEG signal, and safety, since no DC current is drawn from the patient. Additionally, these electrodes are biocompatible [14, 15]. On the other hand, non-contact EEG electrodes require a very high input impedance and is highly affected by the motion artefact noise [14]. [17, Fig. 3] shows an example of each of the three type of EEG electrodes: wet (ring), dry and non-contact.

Figure 3 - Types of EEG Biopotential Electrodes: (A) Wet electrode, (B) Dry electrode and (C) Non-contact electrode [17].

#### 2.3. Previous Literature

#### 2.3.1. Surface Laplacian in EEG detection

Electroencephalography (EEG) is a non-invasive technique and tool employed for several areas of brain research and hospital diagnoses. Despite its advantages, EEG has a significant disadvantage caused by its poor spatial resolution. This causes blurring effects of the volume conductor and a contamination of the signal since reference electrode problems are produced from the absence of an ideal reference. Nevertheless, some research has been conducted and concludes that the employment of a concentration ring configuration with an increased inter-ring distance can alleviate this problem [18, 2].

By employing the surface Laplacian mathematical analysis and Finite element model Makeyev & Besio demonstrate that increasing the inter-ring distance will provide more accurate Laplacian estimations and decrease the relative and maximum error [2]. However, a practical demonstration of the theoretical findings have not yet been presented. Makeyev & Besio employ the (4n + 1)-point method for to obtain a constant inter-ring electrode distance (n + 1)-polar with n numbers of rings. This approach is based on the use of distance equal to r and the employment of a plane square as shown in [2, Fig. 4] [2]. Furthermore, the (4n + 1)-point method was modified to obtain the increased inter-ring distances. The distances between the rings are set r for the first ring, 2r for the second ring, 3r for the third ring, and so on [2].

Figure 4 - Regular plane squared grid with interpoint distance equal to R used by Makeyev and Besio [2]. Extensive investigation into concentric ring electrodes has been conducted in the past, including the development and testing of a modular active sensor, built using a concentric ring electrode printed on a flexible substrate [19]. An inner disc forms the electrode design, and two concentric ring electrodes which are placed in a bipolar configuration. However, the design was only tested by recording an Electrocardiograph (ECG) signal. Prats et al. found that the flexible electrode showed better performance than rigid electrodes since the flexible electrode presented higher skin-electrode contact. Unfortunately this experiment has only been conducted in the collection of ECG signals which are larger than EEG signals, for which the reliability of collection remains relatively unknown.

#### 2.3.2. Capacitive tilt non-contact electrode design

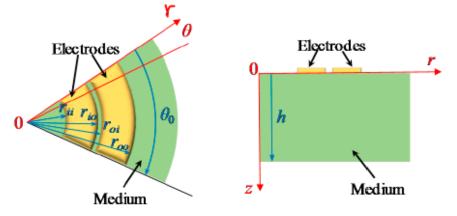

Guo et al. (2016) have also studied the concentric coplanar electrodes, however, unlike Makeyev & Besio, segmented electrodes were used and employed as a capacitive tilt sensor [20]. Guo et al. as Makeyev & Besio, focus on developing the mathematical model by connecting the geometric dimensions to sensor capacitance, the model expressions obtained by employing the Hankel transformation to solve the Laplacian equations. Additionally, Guo et al. employ the Finite element model to evaluate and verify the reliability of the findings [20]. The analytical model of the segmented coplanar sensor was proposed by using two concentric electrodes that have a central angle, and inner and outer radii for the inner and outer ring or segmented electrode as is shown in Figure 5 [20]. For the mathematical model, it was assumed that permittivity of the medium is  $\epsilon$  and the thickness of the medium is *h*. Furthermore, it is assumed that the Laplacian equation  $\Delta \phi = 0$  is satisfied by the potential in the medium. The mathematical and theoretical definition of capacitance can be expressed as in [20, Eq.1]. Guo et al. used this equation to evaluate the mathematical model by employing Finite Element (FE). The results of their research showed that the capacitance of the annular coplanar sensor is linearly proportional to the medium permittivity and the central angle, and the inner annular ring should be wider than the outer annular ring.

$$C = \frac{Q}{\Delta V} = \varepsilon \cdot \theta_{0} \cdot \frac{1}{4\int_{0}^{\infty} \frac{\left[\frac{r_{\rm io}J_{1}\left(\xi r_{\rm io}\right) - r_{\rm ii}J_{1}\left(\xi r_{\rm ii}\right)}{\xi\left(r^{2}_{\rm io} - r^{2}_{\rm ii}\right)} - \frac{r_{\rm oo}J_{1}\left(\xi r_{\rm oo}\right) - r_{\rm oi}J_{1}\left(\xi r_{\rm oi}\right)}{\xi\left(r^{2}_{\rm oo} - r^{2}_{\rm oi}\right)}\right]^{2}}{\tanh(\xi h)} d\xi}$$

Equation 1 analytical calculation of the capacitance [20]

As we can see, many researchers have mathematically demonstrated the reliability of the coplanar concentric sensor to be used for a different purpose, especially in biosignals such as ECG and EEG. Nevertheless, a segmented coplanar which has shown similar mathematical results such as the distance between rings and the width of the ring have been not employed in the collection of bio signals. Therefore one of the primary objectives of this thesis is to build a segmented coplanar ring capacitive electrode with an increase in the ring separation to be used in the collection of EEG signal with the finality to obtain reliable signals that can be used in future research and hospital diagnose as is shown in [20, Fig. 5]. The electrode designed will be an active non-contact capacitive electrode, and the segmentation will act as an individual electrode and as a grid. The segmentations, organisation and dimension of the rings seek to overcome the disadvantage of poor spatial resolution highlighted by previous research. The implementation of the grid in the electrode design is the result of research showing that a grid electrode design can reduce the motion artefact noise, such as conducted by Peng et al. and Wartzek et al.

Figure 6 - Electrode design (Author's own)

Peng et al. present in their publication a design of an active drive shielding electrode with a gridmultilayer; this design was then compared with a different electrode design. This particular experiment shows that the motion artefact and the effects of the signals interferences are lower in comparison with other electrodes that were evaluated [21]. Furthermore, Wartzek, et al. state that an appropriate electrode-body design can reduce motion artefacts, while the use of a grid electrode can help to reduce accumulation charges [22].

#### 2.3.3. Active non-contact electrode design

To obtain design and build an EEG sensor which delivers a reliable signal, a good electrode design is not solely sufficient. It is also necessary to have an efficient electronic design of the stage of amplification, control, and transmission of the signal. Designing a reliable amplification stage is crucial, since EEG signals are very weak at approximately less than 100µV at 100Hz, causing measurement difficulties. Sullivan et al. design a low-noise non-contact EEG/ECG sensor; the low-noise capability was achieved by having an active shield [23].

The circuit design presented by Sullivan et al. employs an instrumentation amplifier due to the low input bias current, typically 3fA. Despite the low current, they decide to implement a reset circuit which includes two transistors and two resistors for the purpose of avoiding high impedances in the input node towards one of the supply rails [23]. The research conducted by Sullivan et al. has allowed the door or new possibilities in the design of integrated non-contact EEG sensors, since it was operational from up to 3mm from the skin. In addition to achieving low noise, another aspect to be considered in the design of a non-contact capacitive sensor is power consumption and the creation of sensor networking. Chi et al. implemented these considerations in the design of a non-contact EEG/ECG sensor [24, 25].

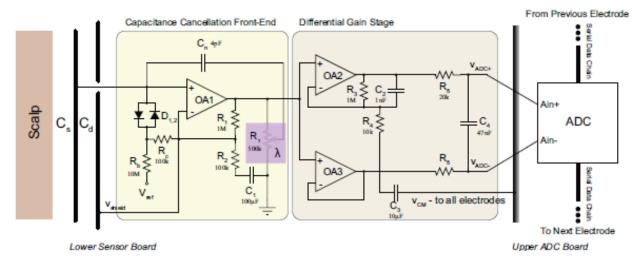

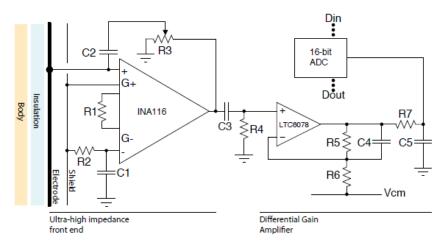

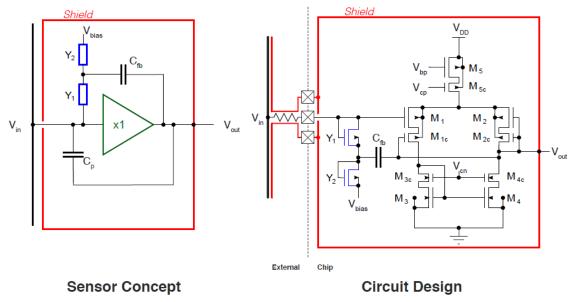

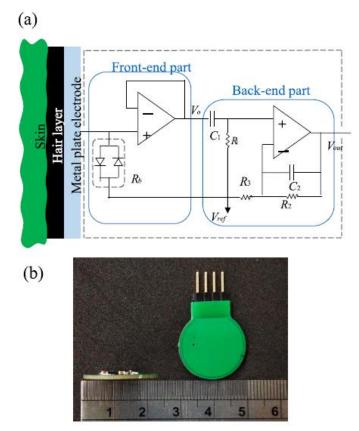

The Chi et al. design consisted of two boards. The first board constitutes of the electrode or sensing plate, the bottom layer of the printed Circuit Board (PCB), and the amplification stage which includes

the capacitive cancellation front end and the differential gain stage. The amplification stage is located in the top layer of the PCB. The second board consists of the analogue to digital converter (ADC) and the data interface, as shown in [25, Fig. 7]. As shown, the gain of the front-end amplification provides impedance conversion and signal gain to the sensor, which was set by the resistors R1 and R2. Furthermore, to ensure the capacitive cancellation and avoid the banding of the gain, the capacitance of the capacitor C1 should be large and the capacitance of the capacitor Cs should lowered [25, 24].

Figure 7 - Micro power Non-contact EEG Electrode with Active Common-Mode Noise suppression and capacitive input cancellation [25]

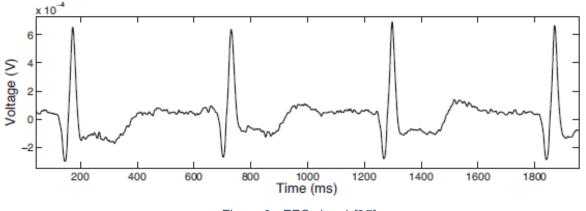

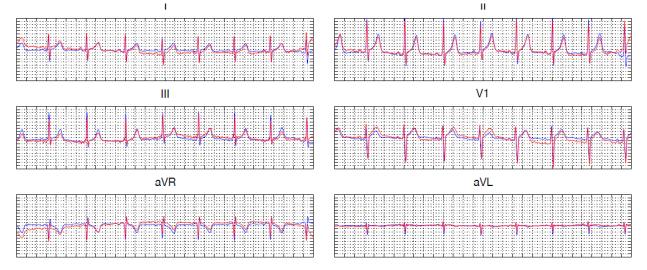

Therefore, it is possible to state that sensor electrode sensitivity, noise levels and channel matching have a high dependence on the front-end stage presented. With this electrode design Chi et al. was able to conclude that by adding the capacitive cancellation circuit, it is possible to eliminate the variations in the gain and the channel mismatch [24, 25]. However as we can see in [25, Fig. 8], the data obtained from the experiment carried out during the sensor test shows that the noise from motion artefact is not entirely cancelled, resulting in an ECC signal that is not completely reliable [24, 25].

Figure 8 - EEC signal [25].

Tests conducted by Chi et al. show some promising results, such as the possibility of implementing a small networking of active capacitive electrode. Further research in 2010 resulted in two new

design of Non-contact EEG/ECG Electrodes for Body Sensor Networks. In this case both designs were wireless systems. The wireless bio-potential instrumentation system designs by Chi, et al. consist of a non-contact capacitive electrode that can function without a direct skin connect.

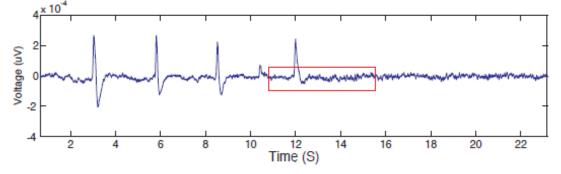

The first design shown in Figure 9 is unlike the designs presented in 2009 as it comprises of an ultrahigh impedance front end implemented using an INA116, and a LTC6078 for the differential gain amplification [26]. In the ultra-high impedance front end, a low pass version of the input to remove the drift and DC offset was used. This low pass version of the input was obtained from the noninverting input and connected to the output. This produced an AC coupling without affecting the input impedance. Also, to maximise the signal swing the output was centred in the mid-rail.

Figure 9 - Schematic of non-contact electrode design [26].

Even though this circuit design had a stronger focus on noise correction, few improvements were made as the noise is not entirely removed and the system is still not completely reliable, as evident in [25, Fig. 10]. The signal is in fact noisier than the one shown in [25, Fig 8]. Further research and design improvements are required to improve the reliability, sensitivity, and noise level of this design.

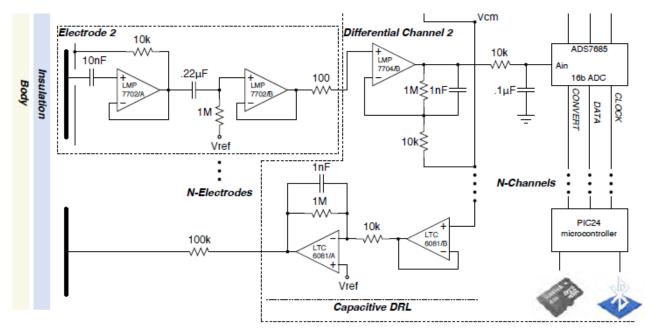

The second design presented in 2010 is shown in [26, Fig. 11]. This is a simpler, replicable and inexpensive design in contrast with the design presented in previous works [27]. As in [26, Fig. 11], the design includes two buffers and a high pass filter stage in the electrode section. The gain stage is formed by a differential amplification stage and low pass filter stage. This design also has a capacitive DRL (drive right leg) electrode with an amplification stage used to reduce the common mode interference [27].

Figure 11 - second EEG schematic deign presented in 2010 [27]

In contrast to previous papers, reference to the subject grounding were utilised due to its necessity in achieving good signal quality [27]. As in [26, Fig. 11], this design employed a capacitive coupling to connect the circuit back to the body, and was implemented using a dummy electrode without components [27]. This method reduces common mode interferences. In addition, the signal obtained by employing this design is clearer than the signal collected by using previous sensor designs due to the combination of the use a battery power system and active ground [27]. However, the result showed that the system is highly sensitive to motion artefacts. As we can see in the results shown in [26, Fig. 12] obtained from the ECG experiments, the signal that shows more sensitivity to motion artefacts is the signal collected using the non-contact electrode [27]. In conclusion, this device still needs improvement the electrode sensitivity to motion artefact and friction to be able to be used in medical grade applications [27].

Figure 12 - Data from the acquired from the ECG experiment (red trace obtained using red dot and the black signal obtained by using Non-contact electrode) [27]

The previous implementation by Chi, et al. used discrete off the shelf amplifiers. The use of this technology presented some disadvantages due to the necessity of tuning input capacitance neutralisation networks manually, while also requiring a complex DC-bias circuit [28]. This led to Chi et al. designing and fabricating a new front end sensor circuit with a custom high input impedance with low noise [28]. The new circuit has an amplifier fully bootstrapped to avoid the use of a capacitive neutralisation circuit. Moreover, it includes an on-chip biasing networking with the purpose to guarantee DC stability and prevent the need for high resistances [28]. [27, Fig. 13] shows the schematic of the front end circuit. The unit gain amplifier in the circuit has functionality, firstly by bootstrapping the parasitic input impedances, and it also maintains a constant voltage across them. The shield is driven by the output of the unity gain amplifier which encloses the trace of the unity gain amplifier input.

Figure 13 - Schematic of the Non-contact sensor front end [28]

To demonstrate the reliability of the new front end sensor circuit, an ECG experiment was conducted where it contrasted the signal obtained by using the non-contact electrode and signal collected by employing an Ag/AgCl electrode [28]. As in [27, Fig. 14], the signal collected by using the new non-contact electrode design is slightly more stable than the previous design [28]. However, the signal presents more noise than the design presented in 2010, shown in [26, Fig. 12].

Figure 14 - samples obtained by using standard Ag/AgCl (blue signal) and Non-contact front end (Red signal) [28].

The new design presented has improvements that allow this circuit to perform slightly better than previous iterations [28]. However it is possible to build higher non-contact electrodes that are much simpler and without the requirement of a big adjustment. Dry and Non-contact EEG electrodes, which do not require direct skin contact or even conductive gel, could be considered as part and enable a brain-computer interface to be used in research and even in clinical diagnosis. Chi et al. decided to conduct an experiment comparing their latest EEG electrode, their dry electrode design, and a typical Ag/AgCl wet electrode within a steady visual evoked potential (SSVEP) BCI (Brain-computer

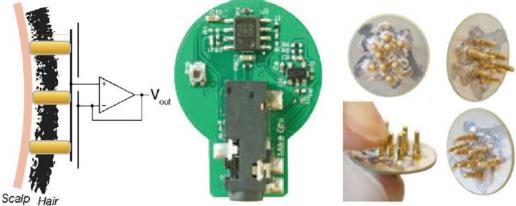

Interface) paradigm [29]. The dry electrode design employ consisted of two parts as in [28, Fig. 15]. The bottom section is formed by spring loaded fingered contact posts that can penetrate the hair and make skin contact without preparation, whereas the top section consists of active buffering circuitry with an off the shelf CMOS-input Operational Amplifier (Op-Amp) [29].

Dry Electrode Concept Active Electrode Circuitry Spring-loaded Dry Contact Pins Figure 15 - concept and implantation of used in the compaction Dry EEG electrode [29]

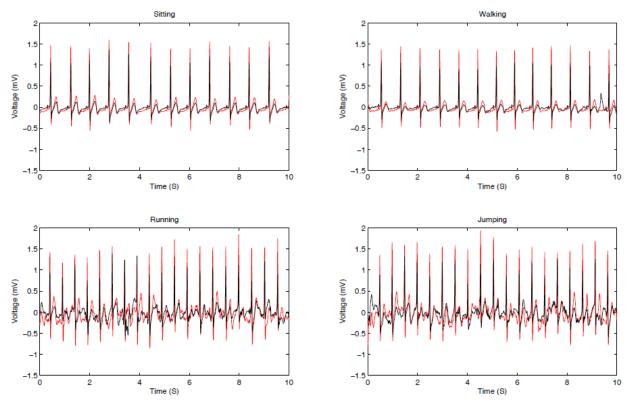

The experiment that was conducted required each subject to guess a single SSVEP target stimulus, displayed on a CRT monitor at 10 Hz for a 1-min duration [29]. Throughout the experiment, a signal from the SSVEP was decoded with the aim of verifying the presence of the stimulus signal [29]. To obtain the best possible dataset, the experiment was conducted three times. The result showed that the electrodes are capable of acquiring an ECG signal due to the signal stimulus being clearly visible for all electrodes as in [28, Fig. 16]. It is also evident that the amplitude of the SSVEP and noise depend on the subject [29]. Moreover, it is noted that the non-contact electrode exhibited a higher amount of low-frequency drift and broadband noise than the dry electrode. The disadvantages observed for the non-contact electrode are unlike the dry electrode due to the high coupling impedance and upper sensitivity to motion artefacts [29]. The experiment also found that unlike the wet electrode, the dry and non-contact electrodes required more time to reach a stable trace [29]. Moreover, they also observed that the signal acquired with dry and non-contact electrodes do not show degradation over time [29].

It is therefore possible to conclude that the non-contact electrodes and the BCI requires greater improvement and care with the design, specifically a non-contact sensor to overcome the EEG level signal problems [29]. Furthermore, the dry and non-contact electrodes can be successfully employed within controlled BCI application [29].

More recent research on non-contact electrodes is offered by Chen et al., presenting a new noncontact EEG electrode design With Adaptive Mechanical Design for Measuring EEG in a Hairy Site [30]. The adaptive mechanical design was conceived with the goal of improving the motion artefact effect. The non-contact sensor design is formed by two parts as in [29, Fig. 17]. The bottom part forms the electrode with a circular copper film, while the top part amplification state consists of the front-end section and back-end section. As in [29, Fig. 17], the front-end of the circuit involves a unitary gain amplifier employed to provide a high input impedance and antiparallel diodes used to avoid use signal attenuation [30]. The back-end of the circuit is a band-pass filter used remove the high-frequency noise and the motion artefact effect [30].

Figure 17 - Non-contact Schematic and prototype [30]

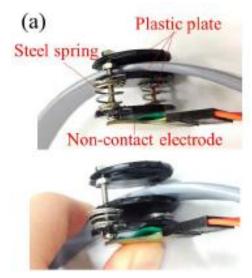

The adaptive mechanical design was located between the sensor and a plastic band. This mechanical design is made up of three plastic plates and steel springs as in [29, Fig. 18] [30]. The flexible band is used as a wearable device, fitted to the head. The spring and plate provide force to maintain the sensor in position and help to reduce the motion artefact effect [30].

Figure 18 - Adaptive mechanical design [30]

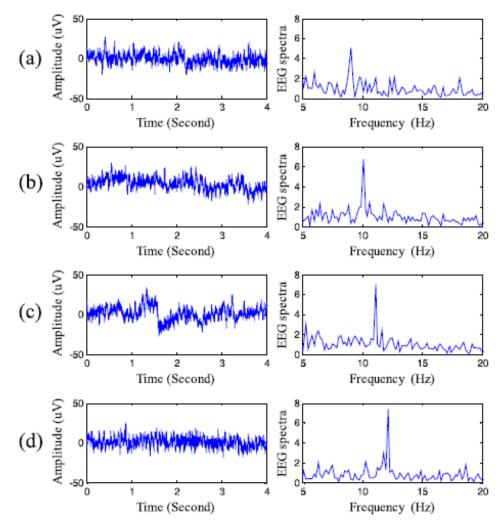

A SSVEP test was conducted in order to evaluate the capability of the sensor with a stimulus signal of different frequencies between 9 and 12Hz, and the non-contact sensor was placed on Oz [30]. As in [29, Fig. 19], the electrode can retrieve the signal from the different stimulus due to the spectrum Vs Frequency graph showing the peak of every frequency [30]. The second most relevant

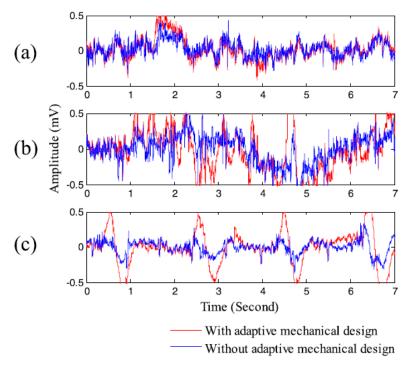

experiment was an EEG measurement under motion artefacts [30]. To clearly observe sensor performance and the mechanical design under motion artefacts, Che et al. placed two pairs of the non-contact sensor on a subject around the Oz location, with and without the mechanical design to acquire EEG signals under different motion conditions [30]. The result of this experiment shows a slight improvement of the signal by employing the adaptive mechanical design. As is presented in [29, Fig. 20], the differences between with and without the adaptive mechanical design is more clearly observed during heavy motion [30]. It is therefore possible to conclude that the adaptive mechanical design minimises the motion artefact effect [30], while simpler designs can prove to provide better results. On the other hand, this design still required improvement in sensibility and reliability [30].

Figure 19 - EEG signal and spectra detected by the non-contact sensor for the SSVEP experiment [30].

The non-contact sensors presented showed improvements in their circuit design and therefore an improvement in performance for implementation time, signal collection, and signal reliability. However the electrodes used in each design were of the same circular copper plate which may be the cause of the persistent noise issues. It was also possible to observe that almost all front end designs were overly complex, causing an increase to the size of the front stage. It is possible that the circuit required does not need to be so complex and may allow for a smaller front stage.

# 3. Project Scope

#### 3.1. Objective

This thesis aims to design a non-contact active capacitive EEG electrode which improves the accuracy of the Laplacian estimation. The goal of this new electrode design is to improve the recording of brain signals by improving noise performance (artefact rejection) and therefore obtaining a more reliable signal for clinic diagnosis and future research examining the possibility of detecting and isolating motor and sensory inputs from the body. This project designs and develops an active non-contact segmented coplanar ring capacitive electrode. The BCI system measure and transmits the EEG signal via Bluetooth. This new model incorporates design elements such as multiple signals from the same area, portability, and wireless bio-signal recording.

The tripolar concentering ring electrode (TCRE) mathematically proven in [2] will be improved using a segmented variation. The electrode design will be powered by a single rechargeable coin cell battery in each sensor, and rechargeable by using a BLE chip feature. The non-contact EEG active Multielectrode prototype will record a reliable EEG signal, and with a BCI system, transmit the EEG signal via Bluetooth. The electrode design incorporates the idea of a tripolar concentering ring electrode (TCRE) to take advantage its ability to automatically achieve the surface Laplacian. Additionally, the TCRE obtains a bipolar difference of the surface potential from the rings that form the electrode [2, 31]. The new EEG electrode will contribute to, and be the base of, a new design and research aiming to improve non-invasive EEG signal collection.

#### 3.2. Requirements

The criteria that should be utilised in order to guarantee the success of the prototype device are:

- The device is portable and battery powered;

- The electrode is an active and capacitive (not requiring conductive gel);

- Wireless bio-signal recording networking/BCI;

- Setup time of the device is less than conventional electrodes;

- The device detects and distinguishes motor and sensory inputs from the body;

- The electrode design provides artefact attenuation; and

- The electrode design improves the accuracy Laplacian estimation.

#### 3.2.1. Procedure and Deliverables

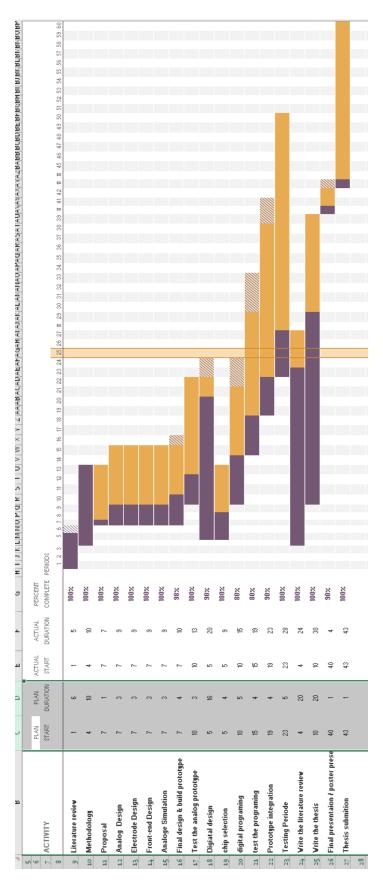

To be able to complete the project on time and fulfil the stated requirements, a Gantt chart shown under Appendix A was designed, stating the deliverables and the time that each deliverable will take. The main deliverables consist of an electrode design and its amplification stage, the analogue to digital PCBs, Bluetooth hardware, and the software design.

# 4. Methodology

The thesis first conducted a literature review on EEG, how it is measured, the type of electrodes commonly used and the previous research. The literature related to EEG is already extensive and therefore is a well-documented field of research. After having conducted the literature review and collating the necessary information, the focus changed the technical aspect of the project, such as the design to be used, suitability of components, and the technical information to be employed in the development of the thesis.

The first stage of the hardware design involved deciding which type of electrode is most appropriate, how it will be built, its capabilities, and its limitations. After deciding upon the type of electrode design and during the initial design phase, the complete system design was developed taking into consideration the hardware components available on the market. The hardware selection and design were modified due to the availability of new BLEs with more features such a size decrease and charging option. The selection of the actual components and the system design was based on technical documentation of the components and previews works.

The second stage of the hardware design was the development of the amplification stage for the electrodes, the front-end, and traditional circuits. After completing the initial circuit designs, they were presented to, and discussed with, supervisor Professor Powers and met his approval, allowing the design of the PCB to continue.

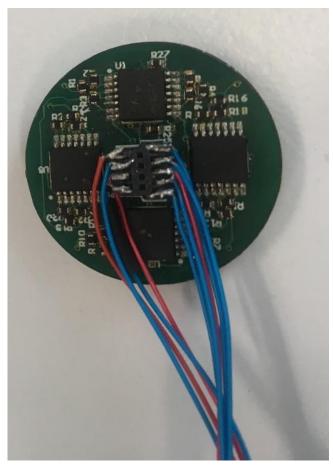

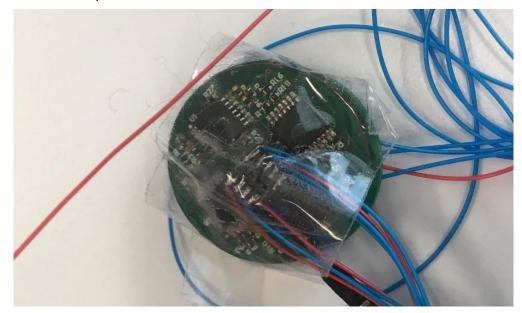

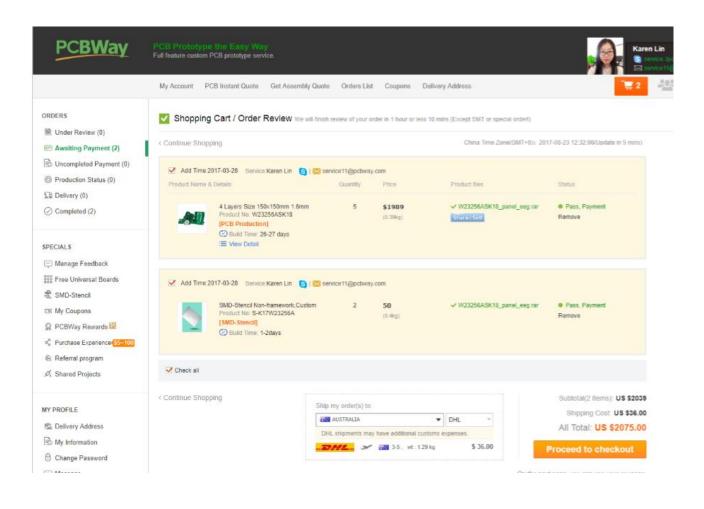

After obtaining approval of the circuit design, the PCBs were developed while the BLE was being programmed. A few iterations of the PCB's design were developed during the process. This was conducted so that focus was on one section at a time, and that each completed stage was integrated, such as the electrode and its readout circuit. The approach was focussed primarily to the electrode design and its build. Due to time and budgetary constraints, the ADC and BLE were designed only, and are in the process of being assembled.

# 5. Design Overview

To show a better and clearer view of the whole system, a design overview is presented to give a perspective of the prototype development and a see how it may operate after completion. From the project scope, it is possible to derive three major design sections which required development: the electrode, the front-end, and the output system.

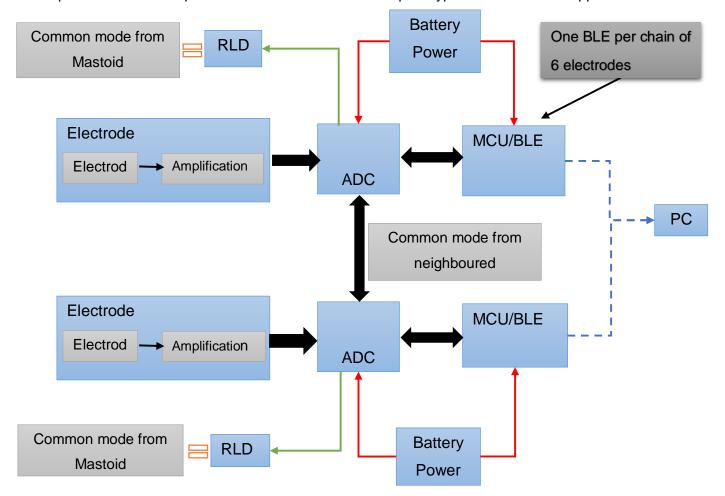

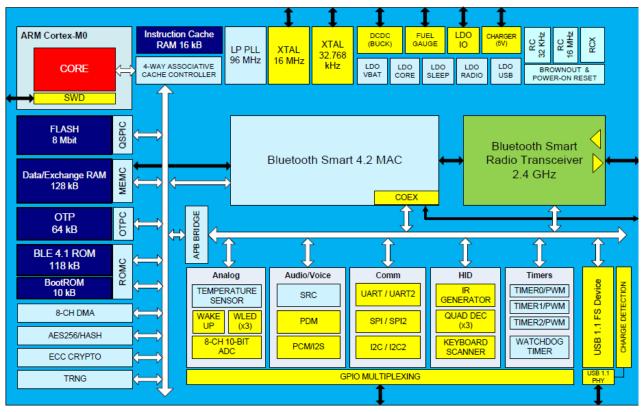

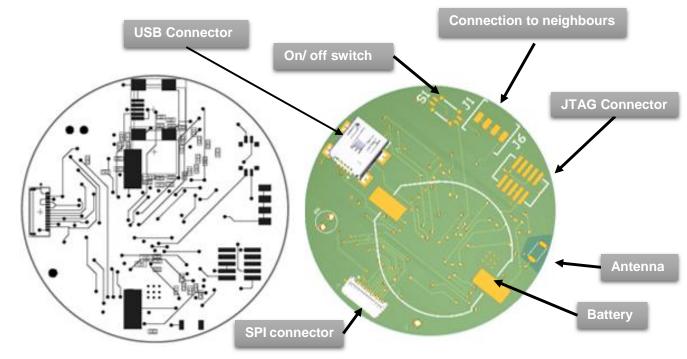

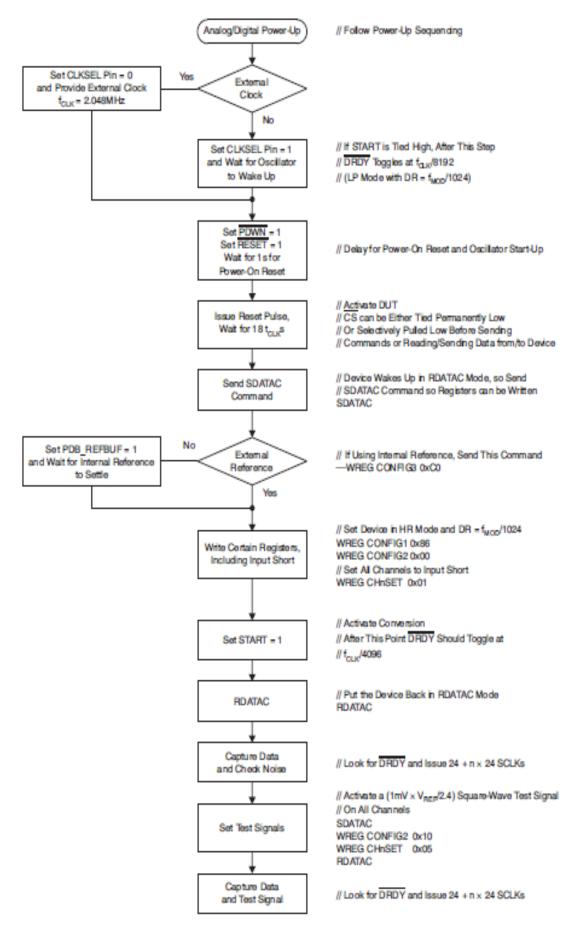

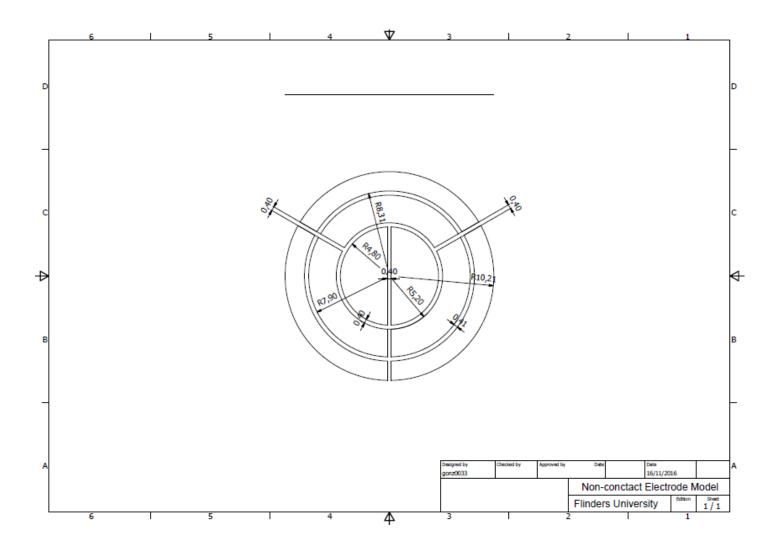

Fig. 21 presents a block diagram of the main elements of the last electrode of the EEG device prototype which permits the EEG device to operate and perform its functions satisfactorily. The system design constitutes of six heptrodes on an SPI bus feeding one MCU/BLE. The signal is acquired from the scalp of the subject by employing the new EEG electrode designed to the amplification stage, and to the ADC also knows as Analogue Front End (AFE). The ADC or AFE quantises the signal acquired to be transmitted through a BLE system via Bluetooth to a computer. A complete list of the components used in the EEG device prototype can be found in Appendix B.

Figure 21 - Block diagram of non-contact EEG active Multielectrode Hardware Design (Author's own)

# 6. Non-Contact Electrode

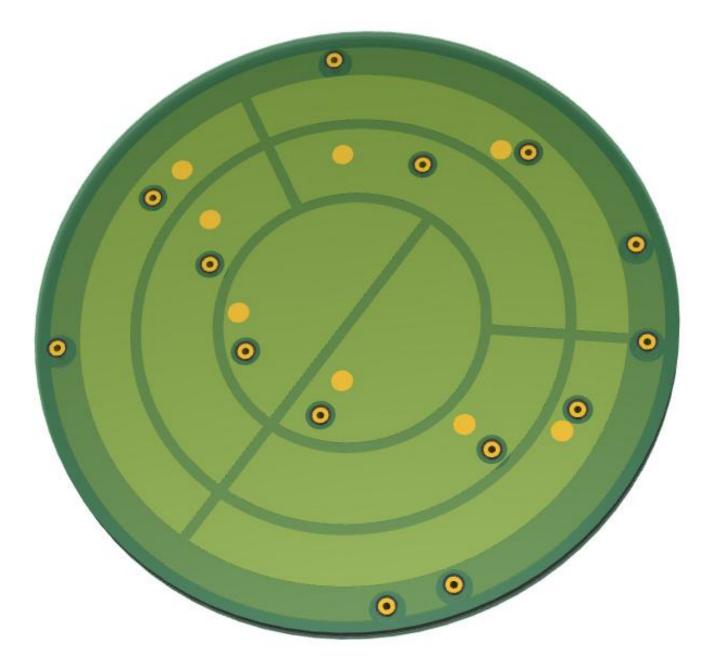

Conventional wet (gel) and dry electrodes are widely employed for biopotential measurements such ECG and EEG, despite their disadvantages such as long preparation time, discomfort, pain, and skin irritation. The work presented in the paper consists of the design and development of a non-contact capacitive electrode prototype for EEG signal collection which does not suffer from these disadvantages. The new electrode design concept lies between the variable inter-ring distance concentric ring electrode [2], and a segment annular coplanar capacitive tilt sensor [20], allowing the advantages of both to be utilised and addressing most of the disadvantages. The new electrode design is a segmented tripolar capacitive electrode. This non-contact electrode would improve the accuracy of the Laplacian estimation, provide artefact attenuation, and detect and distinguish motor and sensory inputs from the body. In addition, this design enhances the spatial resolution of this type of electrode via an increase in the ring separation, while the ring is a smaller diameter (inner ring 9.6mm, second ring 15.8 mm and external ring 20.4 mm) compared to previous non-contact active electrodes (22.5mm to 24.26mm). One of the most relevant characteristics of non-contact electrodes is their ability to act as a capacitor between the body and the readout interface, allowing for remote sensing (without direct skin or scalp contact) [14]. Furthermore, the readout circuit should be located near to the electrode.

#### 6.1. Material use in electrodes and their Chemistry

One key factor that should be considered when attempting to obtain a reliable signal from an EEG electrode is the electrochemical properties of the materials employed in the electrode construction and coating that is used [32]. This can significantly affect the quality of the EEG measurement [32]. Additionally, the knowledge of the interaction between the electrode-electrolyte interfaces is fundamental for the development of the electrode and the analysis of its performance [32]. Since the non-contact electrode, like the dry electrode, does not require conductive gel, the material employed on the surface of the electrode dictates performance in respect to contact impedance and noise [32]. The recording of low-frequency components is particularly challenging due to contamination by noise and drift in the half-cell potential [32]. [31, Tab. 2] shows a summary of different possible materials and their respective performance. Silver/silver chloride (Ag/AgCl), silver, and gold are shown to offer the best performance to employ in an EEG electrode [32]. The plate electrode is the most commonly used electrode in non-contact EEG design. To our knowledge, tripolar concentric ring electrodes (TCRE) and tilt electrodes have not yet been utilised and considered in non-contact EEG recording.

| Material           | Offset Voltage, Resistance and Polarization | Rate of Drift | Noise Level |

|--------------------|---------------------------------------------|---------------|-------------|

| Sintered Ag/AgCl   | Very low                                    | Very low      | Low         |

| Disposable Ag/AgCl | Low                                         | Very low      | Low         |

| Silver             | Variable                                    | Variable      | Low         |

| Gold-Plated Silver | Variable                                    | Variable      | Low         |

| Platinum           | Very high                                   | _             | Low         |

| Stainless Steel    | Very high                                   | _             | Medium      |

| Tin                | High                                        | High          | High        |

Table 2 - Electrode performance is employing a different material for coating [32].

### 6.2. Electrode Design

This design attempts to overcome the clear disadvantages associated with common electrodes and non-contact electrodes such as poor accuracy for Laplacian estimation, long setup time, and low artefact noise reflection. This design is based on the mathematics developed in [2] and [20]. Both papers present similar ideas on electrode performance improvements by varying the distance of the concentric rings. However, the mathematical proof developed is quite different to each other, as detailed in Section 2.

The design presented here considers a concentric ring electrode configuration with the variable interring distance that increases linearly from the central disc, as the concentric ring electrodes are theorised to provide a more accurate and reliable surface Laplacian estimation relative to constant inter-ring distances alternatives. The segmentations on the electrodes rings are implemented into the design with the intent to increase the communication rate of the EEG, obtain multiple signals from the same electrode area, provide greater artefact attenuation and attempt to detect and distinguish the motor and sensory inputs from the body.

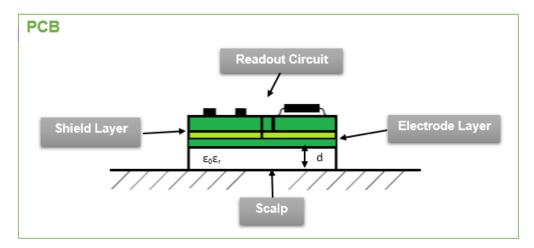

#### 6.3. Shape Design

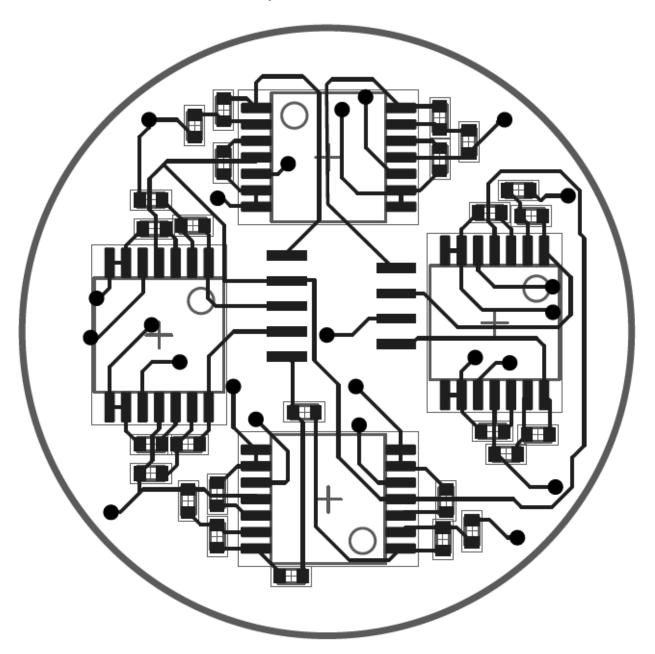

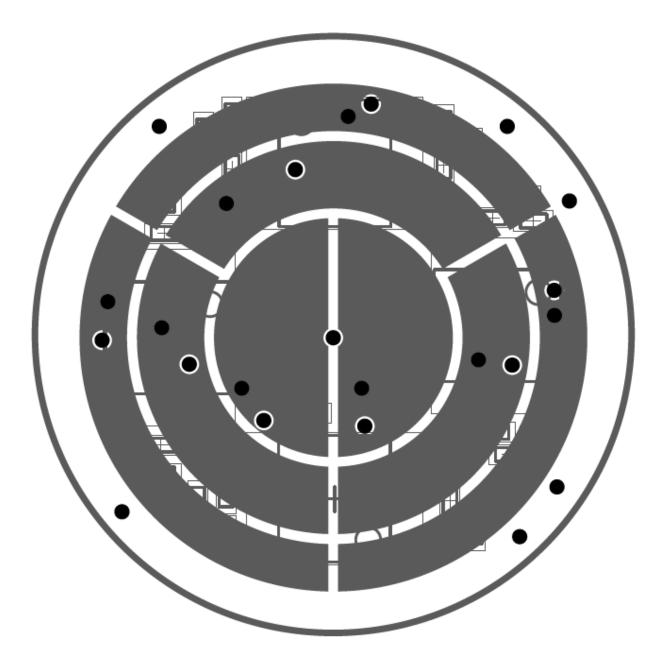

The capacitive electrode was built as a parallel layer, four metallic layers separated by dielectric material and two ground layers. Both layers were composed of the metal layer on a PCB and the scalp of the patient. The previous setup described is shown in [Fig. 22]. The capacitance of the parallel-plate capacitor is defined in [ [33], EQ. 2] where A is the area of the plate, D is the separation between the plates,  $\varepsilon_r$  is the relative static permittivity, and  $\varepsilon_0$  is the permittivity of the free space.

$$C = \frac{\varepsilon_r \varepsilon_0 A}{D}$$

#### Equation 2 Capacitance [33].

In this type of capacitor, two of the variables vary with the location of the electrode on the surface of the subject body, the separation between the electrode and the skin and the dielectric relative static permittivity, making it difficult to obtain the precise value of the capacitance of the electrode. Many constants form the dielectric relative static permittivity such as the solder mask, the hair, and the sweat on the skin.

Figure 22 - Cross-section of the capacitive electrode PCB (Author's own)

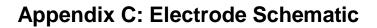

[Fig. 22] shows a schematic of an active capacitive EEG sensor with different levels (layers) such as the electrode layer and the front end amplification. The model of the electrode shape was designed using the software 'Inventor' as in [Fig. 6], which was then imported to 'Altium Designer' to design the PCB of the electrode as in Appendix C. To connect the electrode layer and shield with the readout circuit, vias were place to penetrate the amplification PCB and vias on the electrode layer and pads on the shield layer. Finally, the EEG sensor stages, amplification PCB, and electrode PCB are soldered together. The electrode consisted of two concentric rings and a central disc which are considered as a ring, hence the name TCRE. The two rings and the inner disc were designed to have the same area while there was an increase in the inter-ring separation as mentioned in Section 2.3. Each ring is divided into three segments, and the inner disc in two segments, giving a total of eight pads with the same area.

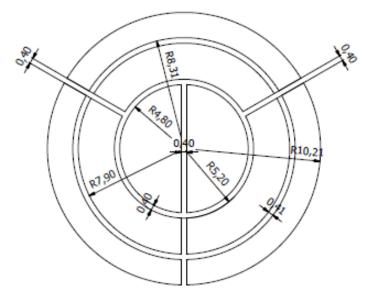

Despite the difficulties, the capacitance was mathematically estimated obtaining a capacitance per each pad of the electrodes approximately of 9pf. The advatcge of having a capacitance higher than 1pf is that at higher capacitange the degradation of the noise performance decrease. This design used 0.4mm spacing at 0.6 mm units in the scaling cell up top. With this design, it was possible to achieve 9pF for each of the eight pads. However, it can be increased by 1.5% as we move out to the spherical part of the head. Under Appendix C the electrode and the model diagram with the dimensions of each ring and pads can be found. [Tab. 3] shows the area and dimensions of each ring and segment, in addition to the value of the filtering caused by resistive bias using the 9pF input model and ignoring scalp resistance and skin impedance.

| 3-Ring-<br>Electrode | Unit<br>size | 0                | .6 mm             | Between<br>Ring | Pad as proportion<br>of ring |                 |                                 |                           |                | %ring      |

|----------------------|--------------|------------------|-------------------|-----------------|------------------------------|-----------------|---------------------------------|---------------------------|----------------|------------|

| Radius<br>(mm)       | Delta        | Diameter<br>(mm) | Pad + Gap<br>Area |                 | Gap Size (mm)                | Segment<br>Area | Capacitance                     | Bias<br>Resistance        | @0.159Hz       | Hz<br>knee |

| 2.40                 | 2.40         | 9.6              | 72.38             | 0.399           | 0.40                         | 35.8            | 8.95 pf                         | 223.5145875               | GΩ             | 98.9%      |

| 6.54                 | 1.34         | 15.8             | 110.18            | 0.409           | 0.40                         | 36.3            | 9.08 pf                         | 220.211216 G              | Ω              | 98.9%      |

| 9.25                 | 0.96         | 20.4             | 111.87            |                 | 0.40                         | 36.9            | 9.22 pf                         | 216.8564124               | GΩ             | 98.9%      |

|                      |              |                  |                   |                 |                              |                 | 0.32Hz & cent                   | plit to both rai          |                |            |

|                      |              |                  |                   |                 |                              |                 | (33GΩ±20% s<br>0.96Hz & cent    | plit to both rai<br>tres) | Is low cut fil | ters at    |

|                      |              |                  |                   |                 |                              |                 | (10pF±5% spl<br>without filteri | it to both rails<br>ng)   | centres acc    | urately    |

Table 3 - Dimension, ring separation, and capacitance calculation of the electrode (Author's own)

#### 6.4. Capacitance

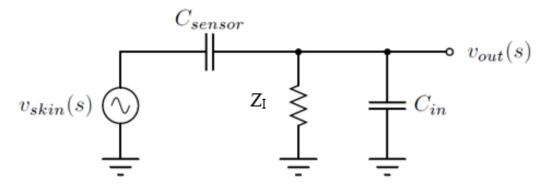

This section presents the circuit theory behind of the capacitive electrode; the aim is to create a capacitance between the surface of the scalp or skin and the readout circuit with the finality of collecting the biopotential signal generated by the body. The capacitive electrode acts as a high pass filter due to the capacitor create high impedance to DC voltage with input Residence. The circuit schematic of the capacitive electrode if shown in [34, Fig. 23].

Figure 23 - Schematic of the capacitive electrode [34]

The Cin on the circuit shown in [34, Fig. 23] refers to the capacitance seen in op-amp output, the Zi is the input resistance of the Op-amp, and the Csensor is the capacitance of the electrode. By conducting an AC, the analysis was obtained the transfer function of the circuit as shown below showing the high-pass filter nature.

$$V_{out}(s) = \frac{Z_{i} \parallel \frac{1}{sC_{in}}}{\frac{1}{sC_{sensor}} + \left(Z_{i} \parallel \frac{1}{sC_{in}}\right)} * V_{skin}(s)$$

Equation 3 Voltage output of the electrode [35].

Applying some algebra was obtained that the transfer function of the electrode is:

$$H(s) = \frac{V_{out}(s)}{V_{skin}(s)} = \frac{C_{sensor}}{C_{sensor} + C_{in}} * \frac{s}{s + w_0}$$

Equation 4 - Transfer function of the electrode [35].

$$w_0 = \frac{1}{Z_i(C_{sensor} + C_{in})}$$

#### Equation 5 - Cut-off frequency of the filter [35].

As we can see in [35, Eq. 4], there is a constant loss in the pass band of the filter. This loss depends on the value of the capacitance and whether the capacitance decreases in the order of magnitude of the input capacitance. The loss in the pass band can be 10% or more of the signal amplitude.

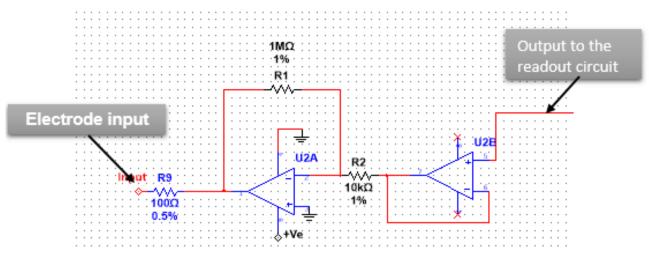

### 6.5. Amplification (Readout Circuit)

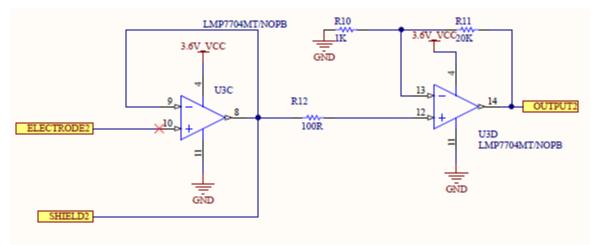

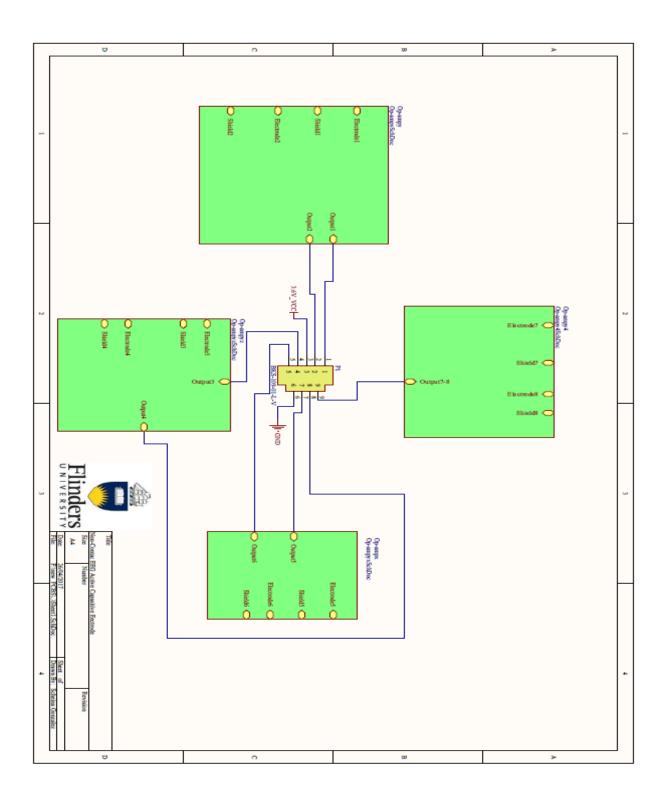

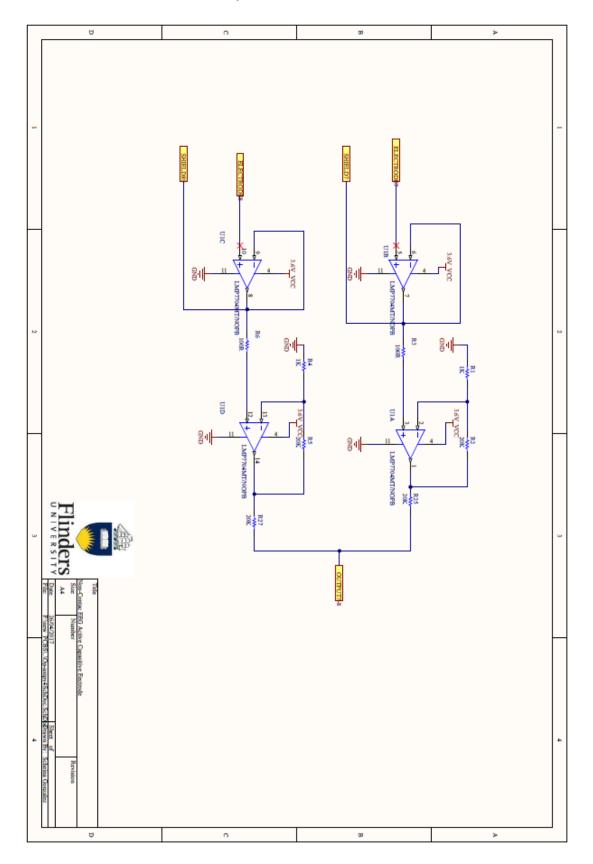

As previously in [14, 16, Tab. 1], the Non-contact capacitive electrode must be an active electrode with the ability to buffer the signal and totally or partial avoid external noise. The readout amplification level consists of a buffer level and a gain level. The completed schematic circuit is shown in [Fig. 24]. The readout circuit is implemented on each pad of the electrode and is shown under Appendix D.

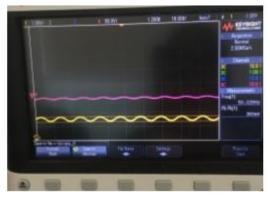

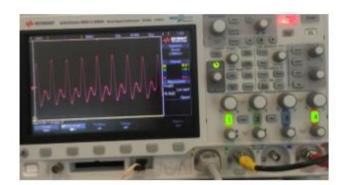

Figure 24 Schematic circuit of the Readout amplification circuit (Author's own)

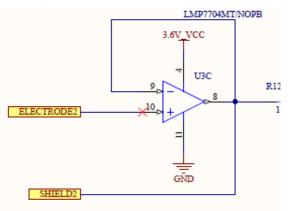

### 6.5.1. Circuit Design

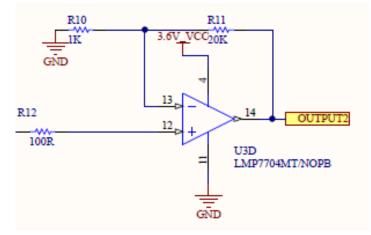

The operational amplifier used is the LMP7704 by Texas Instruments. This component was utilised in the circuit design since it is a precision amplifier, and a rail-to-rail input and output that reduces the CMRR glitch commonly associated with rail-to-rail input amplifiers. B and C Op-Amps are configured as a buffer or unity gain voltage buffer. By using this Op-amp and this configuration, it is not necessary to implement an external input network. Also, the inputs systematically charge, and are maintained within the rail-to-rail input range when used. By the same process, the buffer level output is also stable since, as previously noted, the LMP7704 has rail-to-rail outputs, and a buffer configuration in the lower readout circuit level. Moreover, this allows for a favourable performance due to a bias network introducing noise and degrading the input impedance. To isolate the buffer stage from the gain stage, a  $100\Omega$  resistor was placed between them. A significant advantage of having a buffer stage is that it is no longer necessary to have precisely matched passive components in the electrode level for a good common-mode rejection ratio (CMRR) [26]. The op-amps A and D of the LMP7704 constitute the gain stage of the readout amplification circuit. This two op-amp are

Scheina Gonzalez: Non-Contact EEG active Multielectrode Hardware Design

configured as non-inverters as is shown in [Fig 24]. The circuit was set with a gain of 21, while the analysis of this circuit is shown in section 6.4.2.

### 6.5.2. Follower Stage Analysis

As in [Fig25], the circuit is a unity gain amplifier or follower. Since the input signal V<sub>1</sub> is found at the positive input of the Op-amp, and the rule states that "when the op-amp output is in the linear range, the two input terminals are the same voltage" [15], V<sub>i</sub> must be seen at the negative input. Output V<sub>o</sub> of the op-amp is also connected to the negative input and the output is therefore equal to the input (V<sub>o</sub>=V<sub>i</sub>), or the output follows the input.

Figure 25 Buffer stage of the readout circuit (Author's own)

### 6.5.3. Non-Inverter Stage Analysis

As in [Fig. 26], the circuit is a non-inverter operational amplifier with a gain of 21. To analyse this circuit and show how the gain was obtained, it is necessary to use the two basic rules for the design of op-amps circuits:

- "when the op-amp output is in the linear range, the two input terminals are the same voltage" [15].

- 2. "no current flow into either input terminal of the Op-amp" [15].

### $V_{12} = V_{13}$ Equation 6 - Op-amp rule 1 [15]

$V_{12}$  appears at the negative input  $V_{13}$  of the op-amp. This cause current i shown in [Eq. 7]. To follow the ground, the current i cannot come from the negative input of the circuit. Therefore, the current i must flow through the resistance  $R_{11}$ . Now it possible to calculate  $V_0$  as is shown in Equation 8 and solve for the gain as shown in Equation 9.

$$\begin{split} i &= \frac{V_{13}}{R_{10}} \\ \text{Equation 7 - Current i} \\ V_{o} &= i(R_{11}+R_{10}) \\ \text{Equation 8 - Output Voltage Vo} \end{split}$$

$$\frac{V_o}{V_{in}} = \frac{i(R_{11} + R_{10})}{iR_{10}} = \frac{R_{11} + R_{10}}{R_{10}} = \frac{20K\Omega + 1K\Omega}{1K\Omega} = 21$$

Equation 9 - Non-inverter stage transfer function and Gain calculation

Figure 26 - Gain stage of the read-out Circuit (Author's own)

# 7. Analogue Front Ends (AFEs) for Biopotential Measurements

For an efficient and reliable interconnection between the sensor stage and the microcontroller stage of a circuit design, it is necessary to have an intermediate stage which allows for a conversion of the analogical signal obtained by the sensor into a digital signal [36]. In addition, this intermediate stage should be able to condition and filter the signal to remove noise and add amplification to weak signals such as physiological signals [36]. This chapter presents a brief discussion of the concept of the analogue front end and its applicability to this work.

### 7.1. AFEs concept

The AFE is comprised of analogue signal conditioning circuits combining amplification, filtering, and in some cases a specific application for sensors [36, 37, 38]. This device can perform many functions, strictly depending on the application for which is used. For example in this work, the AFE was employed to condition the EEG analogue signal to be later transformed into its digital representation. The AFE can be connected directly to a microcontroller or microprocessor by a standard serial communication. Another important feature of AFE is scalability as it has enough ports to be able to connect multiple sensors reduce the size of the circuit board, decrease the component require and improve the power consumption [36, 37, 38].

### 7.2. AFE specification requirement

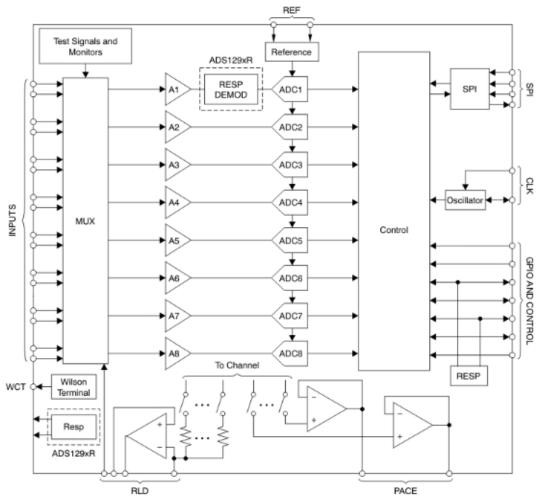

To select the appropriate AFE component for the EEG signal acquisition, it was necessary to set some requirements to refine the options. During the research conducted to find the most suitable AFE for an EEG signal, only two components were found, the ADS1298 and ADS1299, offered the best alternative and flexibility that satisfied the following requirements conditions:

- High scalability

- Minimum eight differential channels.

- Daisy chain capability.

- Programmable gain.

- RLD option.

- High input impedance.

- Height resolution

- Low Input Referred Noise.

- High Common Mode Rejection Ratio.

## 7.3. Types of Analogue to Digital Converters (ADC)

The ADC receives an analogue signal and converts it signal into a digital value that can be read by a microcontroller and microprocessor [39]. The two most commonly used ADC architectures are

Delta-sigma ( $\Delta\Sigma$ ), Successive Approximation (SAR). Each architecture has advantages and disadvantages that are briefly presented below, as they were considered for the ADC selection [39].

#### 7.3.1. Delta Sigma ( $\Delta\Sigma$ )