# Enabling Gigabit IP for Embedded Systems

Nicholas Tsakiris

B. Eng. (Computer Systems) (Honours)Flinders University of South Australia

A Thesis Submitted for the Degree of Masters by Research

Flinders University School of Computer Science, Engineering and Mathematics Adelaide, South Australia

2009

(Submitted 17th February 2009)

Dedicated to my parents for their support and love.

## Abstract

For any practical implementation of chip design, there needs to be a hardware platform available for the purpose of prototyping and implementation of FPGA-based programs, whether they are written in VHDL or Verilog. Communication between the platform and a computer is a useful feature of many hardware solutions as it allows for the capability of regular data transmission between the two devices. Furthermore, the ability to communicate between the platform and a computer at high-speeds requires a specially constructed interface, one that can be modified by the designer at their choosing.

There are a number of commercial packages which provide a hardware platform to perform this task, however there are drawbacks to many of the available options. Some may require special hardware to connect to a computer using proprietary connectors or boards, which increases the cost and reduces the flexibility of any solution. Other options may have limited access to the internal structure of the interface, limiting the ability of the developer to modify the interface to suit their needs. There may be an extra cost to provide the code to the interface, separate from the board, which can also tax design budgets.

This dissertation provides a solution in the form of a Gigabit Ethernet connection with a custom IP/network layer written in VHDL to facilitate the connection. With an increasing number of IP-enabled devices available such as IPTV and set top boxes, the ability to link hardware using Ethernet is very useful and so the development of a lean and capable network layer was considered a suitable focus for the project. The overall goal has been to provide an interface which is cheap, open, robust and efficient, retaining the flexibility a developer might require to modify the code to their needs.

After covering some basic background information about the project, the dissertation looks at the requirements of the board and interface, as well as the alternative interface solutions which were looked at before deciding on Gigabit Ethernet. The protocols used in Ethernet are then covered, with both an explanation of the structure of each and their relevance to the implementation. The Finite State Machines which control operation of the interface are covered in depth, with an explanation of their interconnectivity to each other and how they fit in the data-flow between the computer and the board. Error correction and reliability is discussed, as well as any remaining components critical to the operation of the interface.

Pipelining, the method of design which provides the speed required for Gigabit Ethernet, is covered along with the extra speed optimisation techniques used in the design such as RAM swinging buffers. Testing and synthesis are covered which ensure the design is as robust as possible, both in simulations and in real-world applications. The final design was implemented on a Xilinx Spartan 3 FPGA (XC3S5000-5FG900C) and capable of a maximum speed of 128.287 MHz, which is more than enough to satisfy the requirements of Gigabit Ethernet under a variety of network conditions. The interface code occupies 1,166 slices of logic on the FPGA (3% of the total amount of logic available), making it sufficiently compact to run large projects on the same chip. The core was tested on physical hardware and performed correctly at real line Gigabit speeds. Configuration of the computer along with the method of connecting to the board and transferring data is mentioned, with explanation of the code run on the computer to make this possible. Finally, the dissertation provides an example application through the use of JPEG2000 image compression/decompression. "I Nicholas Tsakiris, certify that this thesis does not incorporate without acknowledgment any material previously submitted for a degree or diploma in any university; and that to the best of my knowledge and belief it does not contain any material previously published or written by another person except where due reference is made in the text."

Candidate:

Nicholas Tsakiris

# Acknowledgements

I would like to thank my supervisor, Professor Greg Knowles, for his invaluable help in getting me through my candidature. To my colleagues at the Flinders University of South Australia, School of Informatics and Engineering, I would like to say a grateful thank you. In particular, to Paul Gardner-Stephen for his help in understanding the intricacies of networking protocols, as well as Geoff Cottrell, Craig Peacock and Terry MacKenzie for their assistance. I would also like to thank the academics and staff of that school for their continual support over the past few years. Finally, I would like to thank my friends and family who have helped me during the period of my candidature.

# Contents

| A        | bstra          | ict    |                             | iii  |

|----------|----------------|--------|-----------------------------|------|

| A        | cknov          | wledge | ements                      | vi   |

| 1        | Intr           | oducti | ion                         | 1    |

|          | 1.1            | FPGA   | As                          | . 3  |

|          | 1.2            | VHDI   | Γ                           | . 4  |

|          | 1.3            | Ethern | $\mathrm{met}$              | . 5  |

|          |                | 1.3.1  | History                     | . 5  |

|          |                | 1.3.2  | Gigabit Ethernet            | . 6  |

| <b>2</b> | $\mathbf{Req}$ | luirem | ients                       | 8    |

|          | 2.1            | High S | ${ m Speed}/{ m Bandwidth}$ | . 8  |

|          | 2.2            | Propo  | osed Solutions              | . 9  |

|          |                | 2.2.1  | USB                         | . 10 |

|          |                | 2.2.2  | PCI-Express                 | . 10 |

|          |                | 2.2.3  | HyperTransport              | . 11 |

|          |                | 2.2.4  | InfiniBand                  | . 13 |

|          |                | 2.2.5  | Ethernet                    | . 15 |

| 3 | $\mathbf{Pro}$ | tocols                              | 16 |

|---|----------------|-------------------------------------|----|

|   | 3.1            | Ethernet                            | 17 |

|   | 3.2            | IP                                  | 18 |

|   |                | 3.2.1 IPv4 vs IPv6                  | 21 |

|   | 3.3            | ICMP                                | 23 |

|   | 3.4            | ARP                                 | 25 |

|   |                | 3.4.1 Manual ARP Entries            | 29 |

|   | 3.5            | ТСР                                 | 31 |

|   | 3.6            | UDP                                 | 35 |

|   | 3.7            | UDP Lite                            | 38 |

| 4 | Imp            | olementation                        | 40 |

|   | 4.1            | Functionality                       | 40 |

|   | 4.2            | Data Flow                           | 41 |

|   | 4.3            | Finite State Machines               | 43 |

|   |                | 4.3.1 RAM                           | 43 |

|   |                | 4.3.2 FIFOs                         | 44 |

|   |                | 4.3.3 fsm_read                      | 45 |

|   |                | 4.3.4 fsm_packgen                   | 50 |

|   |                | 4.3.5 fsm_send                      | 55 |

|   | 4.4            | Reliability/Errors                  | 59 |

|   |                | 4.4.1 Tags                          | 59 |

|   |                | 4.4.2 Corrupted/Unsupported Packets | 61 |

|   |                | 4.4.3 Checksums and CRCs                       | 62  |

|---|----------------|------------------------------------------------|-----|

|   |                |                                                | 02  |

|   | 4.5            | UDP Lite                                       | 62  |

|   | 4.6            | Physical Implementation                        | 64  |

| 5 | Pip            | elining                                        | 68  |

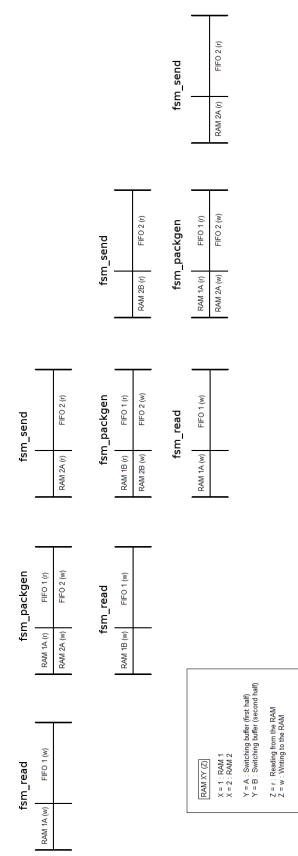

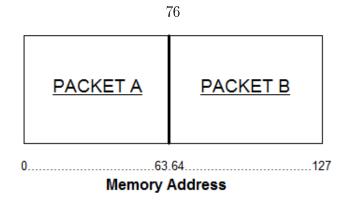

|   | 5.1            | RAM Swinging Buffers                           | 71  |

|   | 5.2            | Timing Diagram                                 | 73  |

|   | 5.3            | Implementation                                 | 74  |

| 6 | $\mathbf{Tes}$ | $\operatorname{ting}/\operatorname{Synthesis}$ | 79  |

|   | 6.1            | Testing                                        | 79  |

|   |                | 6.1.1 Single Packet Tests                      | 79  |

|   |                | 6.1.2 Multiple Packet Tests                    | 81  |

|   |                | 6.1.3 Malformed Packet Testing                 | 88  |

|   | 6.2            | Synthesis                                      | 88  |

| 7 | Cor            | nputer-Side Operation                          | 91  |

|   | 7.1            | Requirements                                   | 91  |

|   |                | 7.1.1 MTU                                      | 92  |

|   | 7.2            | Configuration                                  | 96  |

|   | 7.3            | Operation                                      | 98  |

| 8 | JPI            | EG2000 Core                                    | 105 |

|   | 8.1            | History of JPEG/JPEG2000                       | 106 |

|   | 8.2            | The Wavelet Transform                          | 108 |

|        | 8.2.1   | Lifting Scheme        | . 11 | 4 |

|--------|---------|-----------------------|------|---|

|        | 8.2.2   | Pipelining the Design | . 11 | 8 |

|        | 8.2.3   | Connectivity          | . 12 | 2 |

| 9 Co   | nclusio | n                     | 12   | 5 |

| 9.1    | Futur   | e Improvements        | . 12 | 6 |

|        | 9.1.1   | ARP Support           | . 12 | 6 |

|        | 9.1.2   | IPv6 Support          | . 12 | 6 |

|        | 9.1.3   | TCP support           | . 12 | 7 |

| Biblio | graphy  | 7                     | 12   | 8 |

| Biblio | graphy  | 7                     | 12   | 8 |

| A So   | cket Co | ode                   | 13   | 4 |

# List of Figures

| 2.1 | HyperTransport plug-in card concept                                                           | 12 |

|-----|-----------------------------------------------------------------------------------------------|----|

| 2.2 | External InfiniBand connector (latch type) <sup>1</sup> $\dots \dots \dots \dots \dots \dots$ | 14 |

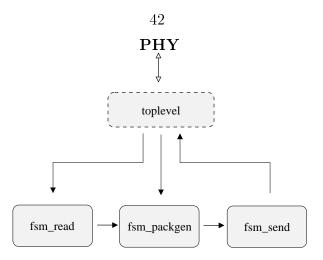

| 4.1 | Flow of data between the various FSMs                                                         | 42 |

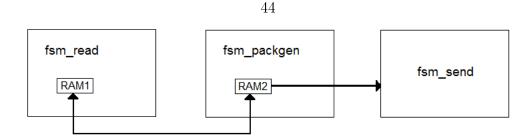

| 4.2 | RAMs used by the interface along with their locations and data paths                          | 44 |

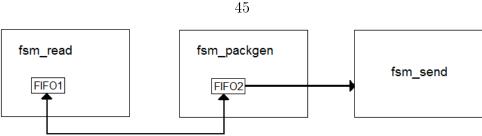

| 4.3 | FIFOs used by the interface along with their locations and data paths                         | 45 |

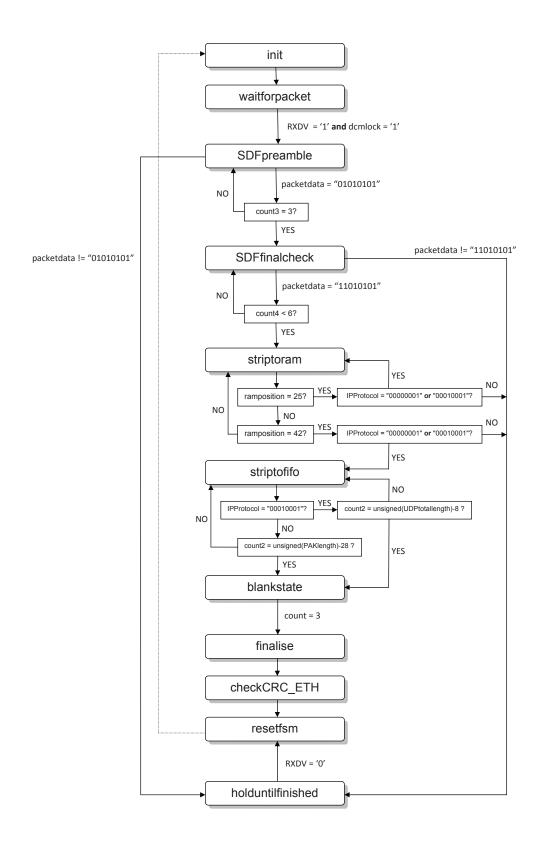

| 4.4 | fsm_read state flowchart                                                                      | 48 |

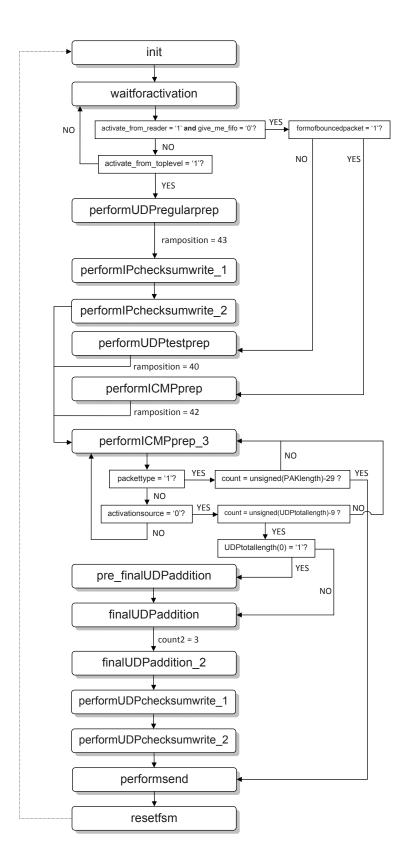

| 4.5 | fsm_packgen state flowchart                                                                   | 52 |

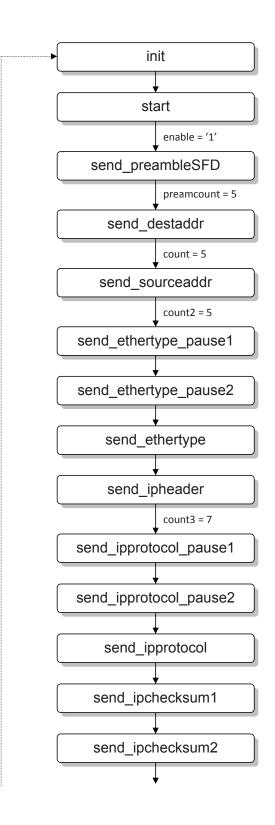

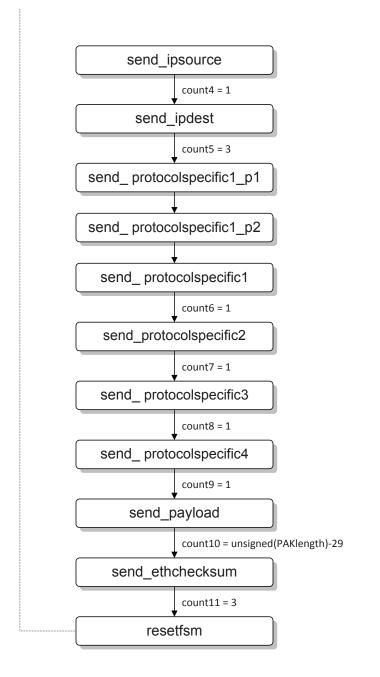

| 4.6 | fsm_send state flowchart (page 1) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$   | 56 |

| 4.7 | fsm_send state flowchart (page 2)                                                             | 57 |

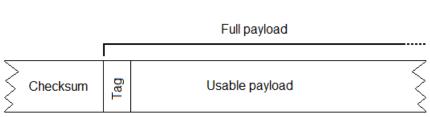

| 4.8 | Fragment of a packet with tag added to beginning of payload $\ldots$ .                        | 60 |

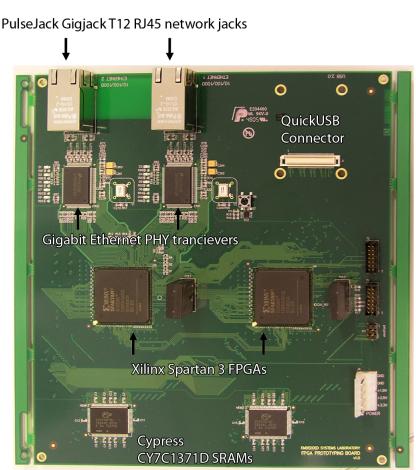

| 4.9 | Prototyping board used for testing                                                            | 65 |

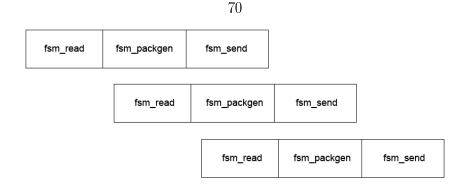

| 5.1 | The three FSMs the single ICMP packet will be processed with (in order)                       | 69 |

| 5.2 | The time-line of three ICMP packets processed in serial                                       | 69 |

| 5.3 | The time-line of three ICMP packets processed in parallel (pipelined) .                       | 70 |

| 5.4 | Timing diagram of three UDP packets in mirrored mode $\ldots$                                 | 75 |

| 5.5 | The locations of two packets in RAM                                                           | 76 |

| 5.6  | Two RAM operations operating at the same time via swinging buffer .    | 78  |

|------|------------------------------------------------------------------------|-----|

| 6.1  | Partial wave table for the beginning of an ICMP packet                 | 81  |

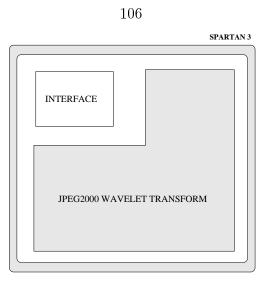

| 8.1  | Space occupied by HDL programs on the FPGA                             | 106 |

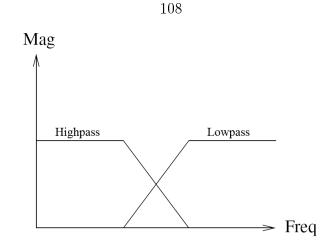

| 8.2  | High and low pass wavelet filters                                      | 108 |

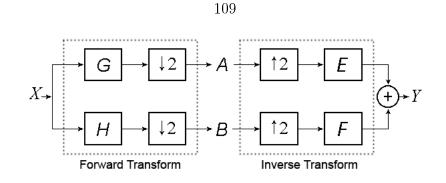

| 8.3  | One-stage wavelet filter bank                                          | 109 |

| 8.4  | Left - Original uncompressed image; Right - One octave wavelet trans-  |     |

|      | formed image                                                           | 110 |

| 8.5  | One octave wavelet transform - quadrant contents                       | 111 |

| 8.6  | Four octave wavelet transform - quadrant contents                      | 113 |

| 8.7  | Daubechies 9/7 Wavelet Transform Equations (Lossy Compression)         | 116 |

| 8.8  | LeGall 5/3 Wavelet Transform Equations (Lossless Compression) $\ldots$ | 116 |

| 8.9  | Symmetric extension at the boundaries                                  | 117 |

| 8.10 | Pipelined execution of the lifting system                              | 119 |

| 8.11 | Hardware lifting blocks in a pipelined architecture                    | 121 |

| 8.12 | Inter-connectivity between system components                           | 123 |

# List of Tables

| 2.1 | Comparison of various communication options                                  | 15  |

|-----|------------------------------------------------------------------------------|-----|

| 3.1 | Structure of a Gigabit Ethernet packet                                       | 17  |

| 3.2 | Structure of the IPv4 header                                                 | 19  |

| 3.3 | Structure of the IPv6 header                                                 | 22  |

| 3.4 | Structure of an ICMP packet                                                  | 24  |

| 3.5 | Structure of an ARP packet                                                   | 26  |

| 3.6 | Structure of a TCP packet                                                    | 32  |

| 3.7 | Structure of a UDP packet                                                    | 36  |

| 3.8 | Structure of the UDP pseudo-header with remaining UDP packet $\ . \ .$       | 37  |

| 3.9 | Structure of a UDP Lite packet                                               | 39  |

| 8.1 | Timing chart for each lifting stage with a sequence of eight values $\ldots$ | 120 |

# Chapter 1

# Introduction

FPGAs (Field-Programmable Gate Arrays) are a useful tool in the electronics industry for constructing prototype designs before mass fabrication onto dedicated hardware and are often used themselves as part of the final design. They are reprogrammable, flexible and extendable, with the capability to run several programs at once and at different speeds. For many designs, interfacing with a computer may be required for data I/O, programming and debugging. If the requirements of the design call for high-speed data transfer with a computer, it is preferable to find some way to accomplish this using an existing interface on the computer, to maximise portability and reduce the dependency on specially-designed hardware.

A particularly common interface on many computers is the Ethernet port, normally used for wired network connections to LANs and WANs. The commonality of this interface makes it ideal for interfacing with an FPGA prototyping board, particularly if both network adaptors involved are capable of Gigabit speeds. However, to actually receive and transmit data using Gigabit Ethernet and have that data available for other programs that reside on the FPGAs is not necessarily straightforward, particularly if one wishes to customise aspects of the interface. There are IP cores available for purchase from several vendors which can provide Gigabit Ethernet functionality for FPGAs, but these generally reside as black-boxes and due to them being distributed as encrypted netlists, do not provide the designer with anything but the inputs and outputs of the core, which makes them unsuitable for the designer who wishes to modify the interface code directly. Sometimes it is possible to obtain the source code for these black-boxes, but the extra cost of the code can add substantially to the overall cost of the IP core. For example, Alcatel provides a fully-featured Gigabit Ethernet core for Altera FPGAs,<sup>2</sup> however costs start at \$30,000 for an encrypted netlist without code. The source code can be purchased, but for an additional cost.

The purpose of this dissertation is to cover the design of a custom IP/network layer, one which has low cost, high reliability and an open structure for easy manipulation. The primary focus was to find an efficient engineering solution to a practical problem, the problem being how to develop the layer to work with low-power devices. Efficient engineering would solve this problem and provide the ability to use low cost hardware to support Gigabit Ethernet line speeds. The design of the core makes it streamlined for typical FPGAs and does not require higher-end hardware.<sup>3,4</sup> The base platform for its design was a Xilinx Spartan 3 FPGA, but the core can be implemented on other FPGAs so long as the base clocking speed of 125 MHz can be obtained. It is not just FPGAs which would benefit from such a design; there are also an increasing number<sup>5</sup> of IP-enabled devices (eg. IPTV, set-top boxes, fridges) which would benefit from a fast and lean network layer without the bloat of extra protocols and functionality which would not be needed in these highly-specialised devices. For this to be achieved, certain features which are available with commercial solutions are not present, but the benefits of a simpler core are evident once the designer has to put the solution to use. The dissertation also covers the physical implementation of the core on realworld hardware as well as the tests performed to validate the core's accuracy and reliability.

Achieving these requirements and solving the problem of an efficient design required some compromises. ARP support was not implemented due to lack of time. TCP support was not implemented due to the fact that the protocol is never implemented entirely in hardware but rather a software/hardware combination using an embedded CPU, which was not available with the sole Spartan 3 FPGA. The Treck TCP/IP core for Xilinx FPGAs is an example of a core which could perform as an offload engine for processing TCP packets, when run on an embedded or soft processor on an FPGA such as MicroBlaze or a PowerPC CPU.<sup>6</sup> However, even with an embedded CPU the size of the core would increase in size and complexity to a level that was not desirable for achieving the lean and clean architecture, which were part of the goals of the design. The lack of packet error detection/correction that is an inherent part of TCP was still provided through the use of tags. The issue of achieving full Gigabit speeds on the base hardware (the Spartan 3) was ultimate the main factor in determining how to construct the core and still satisfy the requirements of the problem.

This chapter introduces several important concepts and ideas which are needed to fully understand the issues raised in this dissertation. Section 1.1 provides a brief introduction into FPGAs, what they are and how they can be used. Section 1.2 explains what VHDL is and what its purpose is with regards to chip design. Finally, Section 1.3 provides a short introduction to Ethernet extending to Gigabit Ethernet and its purpose for this design.

### 1.1 FPGAs

A *field-programmable gate array* is a semiconductor device which contains logic components (also known as logic blocks) which are programmable. By selectively programming the device these logic blocks can function as basic logic gates such as AND, OR, XOR, NOT, or can be extended into more complex combinational functions such as encoders, decoders or simple mathematical functions. Modern FPGAs also contain special logic designed to act as memory elements such as RAMs or FIFOs and depending on the type of FPGA the memory elements may be constructed from flip-flops or dedicated memory blocks on the chip. The key function of an FPGA is to provide the ability to run logic programs with the advantage that the FPGA can be re-programmed multiple times, whereas a regular integrated circuit with support for logic gates would have a fixed design, permanently selected and unable to be altered. Despite being slower than a dedicated chip with a permanent design, FPGAs have a much greater level of flexibility and coupled with the ability to easily be reprogrammed, are ideal for running prototype designs and also for performing multiple tasks with the same hardware.

FPGAs have existed since the mid 1980's when Xilinx released the XC2064, the first FPGA. Despite only supporting a size of 1,000 gates, compared to sizes 10,000 times greater in 2004, this initial form of the FPGA proved very popular.<sup>7</sup> The ability to program the same chip over and over again provided cost-effective design development and increased the development of chip design theory and application. FPGAs have a wide range of applications, from digital signal processors (DSPs) to cryptography and beyond.

### 1.2 VHDL

To program an FPGA, a design-entry language suitable for specifying how the logic blocks interconnect together to perform their tasks is used. For this we use a Hardware Description Language (HDL), which encompasses any computer language specifically designed to formally describe electronic circuits. There are two main languages for this purpose: VHDL and Verilog. VHDL (VHSIC Hardware Description Language, fully expanded as Very-High-Speed Integrated Circuit Hardware Description Language)<sup>8</sup> is the language used by the Gigabit Ethernet project in this dissertation. It is capable of rendering the entire structure of the FPGA including logic, connections and ports and also allows easy simulation capability due to the construction of a testbench. Verilog<sup>9</sup> is another widely-used HDL, but although Verilog is somewhat simpler and easier to code, VHDL was chosen for this design for reasons of familiarity.

### 1.3 Ethernet

### 1.3.1 History

Ethernet is the most common technology used on Local Area Networks (LANs) today. Developed in the 1970s by Xerox Corporation, the experimental version of Ethernet ran at 3 Mbit/s, but the first widespread standard of Ethernet ran at a speed of 10 Mbps in 1985 and later at 100 Mbps (sometimes referred to as *Fast Ethernet*) in 1995, at which point Ethernet had become the regular network system for most computers. The first Ethernet networks, 10BASE5, used thick yellow cable with vampire taps as a medium. Later versions of Ethernet (10BASE2) used thinner coaxial cable with BNC connectors as the connection medium. Currently Ethernet has many varieties that vary both in speed and physical medium used. The most common forms used currently are 10BASE-T, 100BASE-TX and 1000BASE-T. All three utilise twisted pair cables and 8P8C modular connectors, more commonly known as RJ45 (Registered Jack 45) connectors.<sup>10</sup> These forms run at 10 Mbit/s, 100 Mbit/s and 1 Gbit/s speeds respectively.<sup>11</sup>

The RJ45 medium is made from copper cabling, which is suitable for 10BASE-T and 100BASE-TX but can sometimes cause problems with the higher 1000BASE-T form of Ethernet. Due to the significant increase in speed and bandwidth requirements, 1000BASE-T is less tolerable of imperfections in the network cabling than previous standards and electrical noise can potentially degrade a Gigabit connection severely when used with poor-quality or inappropriately specified copper cabling. Most modern Ethernet cabling can support 1000BASE-T satisfactorily, but signal degradation becomes more of a problem the longer the cable becomes. Fibre optic variants of Ethernet are commonly seen connecting buildings or network cabinets in different parts of a building but are rarely seen connected to end systems for cost reasons. Their advantages lie in performance, electrical isolation and distance, up to tens of kilometres with some versions. Fibre cabling is therefore a lot more desirable when dealing with super-fast Ethernet connections such as 1000BASE-SX in a large environment, but is not required in most small networks due to the quality of regular copper cabling.<sup>12</sup>

#### 1.3.2 Gigabit Ethernet

Gigabit Ethernet is a form of the Ethernet standard which allows for high-speed transfers up to one Gigabit per second. The standard was approved by the IEEE in 1998 and later adopted by ISO. The initial standard for Gigabit Ethernet was known as IEEE802.3z, however the most commonly implemented form of Gigabit Ethernet (IEEE 802.3ab) was ratified a year later by the IEEE and uses unshielded twisted pair cabling as opposed to fibre cabling in the initial standard. The reason for the latter standard being more useful is because it allows existing copper cabling infrastructure, used for 10/100 MBit Ethernet, to remain in place without having to be replaced by fibre optic.<sup>13</sup> The fibre version of Gigabit Ethernet is known as 1000BASE-SX and can transmit along a single fibre line at a distance of 500m or more with modern cabling before requiring an endpoint. The unshielded twisted pair variant, 1000BASE-T, generally has a maximum length of 100m. The medium chosen however does not affect the operation of the network layer and is up to the requirements of the environment as to which medium to choose. The same core can be used for either.

Gigabit is the logical successor for 10/100 MBit connections found in virtually all NICs (Network Interface Card) and has stood as a standard for some time and support has become very common, with most motherboards with integrated Ethernet supporting Gigabit, as well as new cards generally supporting it as well. The increase in speed is not only due to the higher clocking speeds (125MHz as opposed to 25MHz in 100 MBit), but also double the transmission bits (8 bits instead of 4). This results in a potential 10 times increase in available bandwidth, which makes it useful for high-speed transfers to and from an FPGA. Furthermore, since Gigabit Ethernet is a common standard, it is trivial to find hardware which can support this standard at a reasonable cost without having to resort to other, more exotic forms of data transfer between an FPGA and a PC.

# Chapter 2

# Requirements

This chapter of the dissertation covers the necessary requirements that precipitated the need for Gigabit Ethernet project. Section 2.1 discusses the purpose of the Xilinx prototyping board and the importance of the high-speed/high-bandwidth requirement. Section 2.2 covers several ideas that were considered before finally settling on the Gigabit Ethernet option.

## 2.1 High Speed/Bandwidth

The origins of this project were in the Embedded Systems Lab in the Engineering department of Flinders University. A characteristic of the work performed by this lab is the data-heavy nature of the designs used, which can range from DNA sorting algorithms to JPEG2000 wavelet transforms to general compression/decompression setups. Speed and bandwidth are essential for performing these tasks; a digital camera, for example, needs to have a fast hardware implementation when performing image compression for storing images to avoid lag time between shots. High clocking speeds allow the circuitry to perform their tasks faster, plus high bandwidth allows a greater amount of data to be processed per clock cycle. Combining the two advantages result in a huge improvement in the capabilities of hardware implementations

compared to their software equivalents, which is what makes hardware designs so attractive for performing specific tasks.

## 2.2 Proposed Solutions

Since data transfer between the FPGA development board and a PC had to satisfy the requirements of high-speed and high-bandwidth, there needed to be a useful way to establish the connection, both at the hardware and software level. Modern computers have a wide variety of different connection standards and the choice to use a specific connection option depends on several factors (some more important than others):

- Performance (the raw speed of the connection, plus maximum bandwidth the connection is capable of)

- Functionality (is any error-correction inherit in the connection standard? is the connection full-duplex? etc.)

- Flexibility (the ability to adjust the way the connection functions, whether through hardware or software)

- Scalability (how capable is the connection method for expanding? can it support newer revisions without changing hardware?)

- Lifespan (how long can we expect to have the connection standard available to us as technology progresses? how quickly will it become obsolete?)

- Commonality (is the connection ubiquitous? can it be found on the majority of computers, or does it require exotic systems?)

- Physical implementation of the connector on the FPGA board (getting the relevant connector working on the FPGA development board must not be par-

ticularly difficult, otherwise the design begins to go beyond the requirements of cost and simplicity)

#### 2.2.1 USB

One option proposed was USB (Universal Serial Bus). USB is extremely common among most modern computers, with the Hi-Speed (2.0) standard supporting a maximum data rate of 480 Mbit/s.<sup>14</sup> However, the two main issues with USB are that the use of high-speed USB requires a maximum cable length of only five meters,<sup>15</sup> which meant the board would have to be linked to the PC fairly closely and though the data rate was fast, there were still faster options available.

#### 2.2.2 PCI-Express

In searching for the fastest connections available to and from a PC, the computer's mainboard is the most logical place to look. Since hardware directly connected to the mainboard will obtain primary access to the system's resources, this results in the highest speed and bandwidth connections available on a PC. A novel idea brie-fly examined was to incorporate the use of a PCI-Express computer expansion card, a standard created by Intel in 2004.<sup>16</sup> The proposal was to specifically use a PCI-Express video card and utilise the dual-DVI (Digital Visual Interface) connectors on the card for raw data transfers. This could be achieved by accessing the video frame buffer, bypassing video-related functions and directly accessing the card's memory to transfer data quickly through the high-speed PCI-Express slot. Using current hardware supporting version 3.0 of the standard, the maximum potential transfer rate for a single PCI-Express slot can be as high as 8 GB/s<sup>17</sup>However, future developments would be hindered somewhat as the DVI standard has stagnated at version 1.0. The Digital Display Working Group which developed the DVI standard has since disban-

ded after the initial release of DVI and so there is no guaranteed upgrade path using the connector, which is why several new standards such as DisplayPort are being established to provide a future connection standard to replace DVI.<sup>18</sup> It was therefore decided that the nature of designing a communications system using a video card's frame buffer would not make it feasible for this design and instead to design this project around a more established standard which could be upgraded in the future with little extra work.

#### 2.2.3 HyperTransport

HyperTransport is an interesting concept in the development of high-bandwidth, lowlatency connectivity solutions. The purpose of the interface is to provide a direct link to the computer's CPU with a focus on bandwidth/latency reduction.<sup>19</sup> Key to the connection is support from the CPU and motherboard chipset to allow this connection to work properly. The primary connection for the HyperTransport interface is known as *HyperTransport eXpansion* (HTX) which utilises uses the same mechanical connector as a typical PCI-Express slot. Further functionality can be obtained through the use of plug-in cards which support direct access to a CPU and DMA access to the system RAM.

The primary advantage of HyperTransport is that it provides a flexible data rate ranging from 200 MHz to 2.6 GHz depending on the HT version used and how it is configured.<sup>20</sup> When run using the full-sized, full-speed 32-bit interconnect, the maximum transfer rate is 41.6 GB/s per link. Obtaining mainboards which support HyperTransport is not difficult, although as of yet only AMD-based systems are capable of supporting the standard; Intel has a competing standard to HyperTransport called *Intel QuickPath Interconnect*, although a practical implementation of *Quick*-

Figure 2.1: HyperTransport plug-in card concept

Path as it is known is not expected to be released until late 2008, too late for the requirements of the project.<sup>21</sup>

An important distinction between other forms of communication with the computer is that by using HyperTransport, the FPGA and relevant hardware must exist on the plug-in card itself. This is unlike other options which use cabling and as such the extra requirements on the design of the FPGA board mean it has to have a physical profile that can fit inside the computer. There is also the issue of limited physical access to the board when the computer case is on, which could cause problems when attempting to view on-board displays or press switches.

There are other ways in which HyperTransport can be used. Instead of plugging a card into an expansion slot, HT modules can be installed directly into a free CPU slot of any compatible multiprocessor motherboard. DRC is a company which supplies plug-in modules supporting this very option; the RPU100 supports a single HT bus along with the Xilinx Vertex 4 LX 60 FPGA. It is inserted directly into a free 940 socket located on a standard AMD Opteron microprocessor motherboard.<sup>22</sup> Multiprocessor motherboards are a requirement when using this direct-access method since the motherboard still requires at least one CPU to run the computer and the HT modules occupy an entire CPU slot without providing the ability for a CPU to

piggyback. This would produce the fastest possible bandwidth capabilities of HyperTransport, but would also further limit physical access to the board and require even more specific (and potentially quite expensive) computer hardware. Given other alternatives available, HyperTransport did not satisfy the needs of the project.

#### 2.2.4 InfiniBand

InfiniBand is a communications technology designed for high-performance architectures, which has made it popular with supercomputers and data centres. It is currently the de facto standard for interconnections with these computing systems.<sup>23</sup> InfiniBand has not made much impact with regular desktop computers in part due to cost, but also the significantly larger bandwidth it provides compared to bandwidth requirements a regular desktop system requires. There are some efforts to adapt InfiniBand as a standard or semi-standard interconnect between low-cost machines as well, plus desktop implementations do already exist in a way which could be used by the FPGA project.

The signalling rate for a single InfiniBand connection is 2.5 GBs in each direction and this can be extended further since InfiniBand supports double (DDR) and quad data (QDR) speeds, for 5 GBs or 10 GBs respectively, at the same data clock rate. However, the standard implements 8B/10B encoding which means that for every 10 bits sent, only 8 bits carry data, so the amount of *useful* data and hence the practical transmission rate is reduced per clock cycle. So, the practical data rates become 2, 4 and 8 GBs for single, double and quad data rates respectively. To increase available bandwidth, links can be combined in banks of InfiniBand connectors, most often together in sets of 4 or 12, called 4X or 12X. A quad-rate 12X link therefore carries 120 Gbit/s raw, or 96 Gbit/s of useful data. Most systems today use either a 4X 2.5Gb/s (SDR) or 5Gb/s (DDR) connection.<sup>24</sup>

Figure 2.2: External InfiniBand connector (latch type)<sup>1</sup>

InfiniBand provides a massive amount of bandwidth, much more than could be expected from any other available solution, however the costs involved and the complexity of implementation would not offset this benefit. Furthermore, for a simple desktop connection it's unlikely that an FPGA would be able to process the massive amount of data at the rates required. Unless several banks of FPGAs processed the data in parallel, the advantages would never be seen. There is also no established standard programming interface for InfiniBand, as the standard only specifies a set of functions that must exist in any implementation, rather than the syntax of these functions which is left to the vendors. The most common to date has been the syntax developed by the *OpenFabrics Alliance*,<sup>25</sup> which has been adopted by most of the InfiniBand vendors and is available for both Linux and Windows (although at the time of writing, not OS X). Also, despite being less costly than some other ultra-high-speed interfaces, InfiniBand is still very expensive and so ultimately, the bandwidth advantages did not sufficiently outweigh the costs, practical implementation problems and lack of platform compatibility that would be useful for the system.

|                          | Bandwidth                                         | Cable Limit              |

|--------------------------|---------------------------------------------------|--------------------------|

| USB (2.0)                | $480 \mathrm{~Mbit/s}$                            | 5 metres                 |

| PCI-Express (DVI medium) | $8  \mathrm{GB/s} \ \mathrm{(Dual \ Link \ DVI)}$ | 4.5 metres (theoretical) |

| HyperTransport           | $41.6  \mathrm{GB/s}$                             | N/A                      |

| InfiniBand               | 96 GB/s (Quad rate, $12X$ )                       | 8 metres                 |

| Ethernet (1000BASE-T)    | $10  \mathrm{GB/s}$                               | 100 metres per segment   |

Table 2.1: Comparison of various communication options

#### 2.2.5 Ethernet

Ethernet became the most appropriate solution at this point, since Ethernet is a very common networking platform and the specifications are easy to source. The RJ45 connectors are also very common, cheap and easy to implement, particularly when using integrated magnetics to avoid adding extra passive components. Gigabit Ethernet provides very high speeds with a maximum data rate of 1 GBit/s, plus it's a very ordered method of packet generation that a state machine written in VHDL would be able to parse without much fuss. A useful feature of Ethernet is that the RJ45 connectors are highly ubiquitous with an established standard which is unlikely to be changed anytime soon. This is important in "future proofing" the core to allow for newer forms of Ethernet to connect to the core, particularly since 10 GBit/s Ethernet has started to increase in uptake among developers of networking hardware.<sup>26</sup> The core can also be reused when 10 G Ethernet in identical between 1 Gb and 10 Gb. The structure of Ethernet and the method for how it is used is documented in the next chapter.

Table 2.1 shows the bandwidth capabilities and maximum cable limits of all the covered communication options.

# Chapter 3

## Protocols

Communication via Ethernet requires the use of an appropriate *protocol* to facilitate the transfer of data. The choice of protocol is very important, as certain protocols are more suitable than others for specific tasks. Some protocols provide extra error correction capabilities which allow for high reliability data transfer, but at the cost of greater complexity in the packet construction/deconstruction. Most protocols have a particular use for them; some are used for testing the capabilities of the data link, some are just for general data transfer, some are used as utility protocols to facilitate communication in others ways. There's quite a lot of flexibility in how to implement communication between two devices and since implementation using FPGAs requires careful use of look-up tables to minimise wasted space and ensure speed requirements for Gigabit speeds, it is vital that only the necessary protocols are implemented, so choosing the appropriate protocols to use is an important part of any implementation. This chapter provides an overview of the common protocols used in the Internet protocol suite and their relevance to the project.

| 7 Bytes                       | 7 Bytes 1 Byte |           |                     | 3 Bytes    | 6 Bytes         |        |

|-------------------------------|----------------|-----------|---------------------|------------|-----------------|--------|

| Preamble Start Frame Delimite |                | Delimiter | Destination Address |            | Source Address  |        |

|                               | 2 Bytes        | 0-9000    | Bytes               | 0-46 Bytes | 4 Bytes         |        |

|                               | Length         | Dat       | a                   | Pad        | Frame Check Sec | quence |

Table 3.1: Structure of a Gigabit Ethernet packet

### 3.1 Ethernet

All the protocols used by the system are encapsulated within an Ethernet packet governed by its own protocol known as the Ethernet protocol. This protocol is important since it holds information that is used to verify whether the packet was transmitted without corrupted or not, as well as where the packet is suppose to be transmitted to in a network. Table 3.1 presents the structure of the Gigabit Ethernet packet. The only difference between the structure of a typical Ethernet packet and a Gigabit Ethernet packet is the size of the Data field - a non-gigabit packet has a maximum size of 1500 bytes, however Gigabit Ethernet can allow for jumbo packets with a maximum size of 9000 bytes. Jumbo packets are covered in Section 7.1.1.

The various fields of the protocol are:

#### Preamble

A sequence of values used to allow the receiver's clock to be synchronised with the sender. For the purpose of the system however, since the synchronisation is controlled using the physical layer and a Digital Clock Manger on the FPGA, the preamble serves the function of alerting the system to the existence of a new packet. All seven bytes are of the form "10101010".

#### **Start Frame Delimiter**

Designates the beginning of the frame and is always "10101011".

#### **Destination Address**

The MAC address of the destination device for the packet.

#### Source Address

The MAC address of the source device for the packet.

#### Length

The length of the data field.

#### Data

The information sent by the packet. For all packets processed by the core, the data field contains the IP protocol, along with an ICMP, UDP or UDP Lite protocol, and then the payload data.

#### Pad

The Ethernet frame requires a minimum size of 64 bytes. Hence, the data field must be at least 46 bytes long to compensate. If the data field is not large enough, the Pad field can be filled with zeros to bring the size up to the minimum required length. No padding is required for the IP core since the combination of protocols used makes the overall packet large enough to satisfy the minimum length.

#### Frame Check Sequence

A CRC used to verify the integrity of the frame.

### 3.2 IP

The Internet Protocol (IP) (RFC 791)<sup>27</sup> is the primary protocol used to send data through a network interface. On its own, IP cannot perform much in the way of

|      | Bits 0 - 3          | 4 - 7          | 8 - 15       | 16 - 18            | 19 - 31         |  |  |  |  |

|------|---------------------|----------------|--------------|--------------------|-----------------|--|--|--|--|

| 0    | Version IHL         |                | TOS/DSCP/ECN | То                 | tal Length      |  |  |  |  |

| 32   |                     | Identif        | ication      | Flags              | Fragment Offset |  |  |  |  |

| 64   | Time to I           | Live           | Protocol     | IP Header Checksum |                 |  |  |  |  |

| 96   |                     | Source Address |              |                    |                 |  |  |  |  |

| 128  | Destination Address |                |              |                    |                 |  |  |  |  |

| 160+ | Data                |                |              |                    |                 |  |  |  |  |

Table 3.2: Structure of the IPv4 header

data transfer as it is more of a organisation protocol, controlling how devices in a network accept the packets which are sent and received. To actually perform useful communication, the protocol is used in conjunction with another network protocol which a specific task in mind. In this respect, IP forms the backbone of much of the communication used in Ethernet. The IP header is of importance in understanding the nature of IP, as it is the part of the protocol that is added to the Ethernet protocol of each packet before any of the other protocols are seen. Table 3.2 presents the structure of the IPv4 header. (Note: there is an optional *options* field which exists at location 160 and run for 32 bits. Options is rarely used by systems and so is not included in the table.)

The Internet Protocol supports a feature called *packet fragmentation* which allows for packets to be broken up and sent in smaller pieces if the MTU (see Section 7.1.1) is too small to hold the entire packet. The core does not support packet fragmentation and as such is not capable of reassembly of fragmented packets. This is not critical because the MTU can be modified to be as large as required by the software run on the computer to interface with the core, so that all packets can be sent without fragmentation. In particular, the core is designed to support *jumbo packets* with a very large MTU (up to 9000 bytes), so fragmentation can be offset by increasing the MTU to the maximum allowed by the network adaptor and ensuring the packets are jumbo sized, but still limited to a size below the MTU to prevent fragmentation. Features related to packet fragmentation such as dealing with out-of-order packets and dropped packets are handled by the tags system as described in 4.4.1.

The various fields of the IPv4 header are:

#### Version

The version of the Internet Protocol. For the purposes of the core this will always be set to 4 (see 3.2.1)

#### IHL (Internet Header Length)

The length of the IP packet header. For all intents and purposes this value is the same between packets. There are occasions where it might be useful to drop particular fields from the header which would result in a shorter header length, but this raises extra complexity for very little gain, so the value here remains constant between packets.

#### Type of Service or DSCP

Used by network hardware such as routers to determine how packets should be transported and queued. Set to 0 by default.

#### **Total Length**

The length of the header and the data. Encompasses the whole packet.

#### Identification, Flags and Fragment Offset

These are used during the process of packet fragmentation. The Identification is a 16bit number which can be used to identify the packet for reassembly, Flags is used to set whether routers can fragment a packet or not and whether there are more fragments for the particular datagram, and Fragment Offset is set by the router performing the fragmentation to assist in recovery of a fragmented packet. Since the core does not use packet fragmentation, these values are simply copied from incoming packets sent by the computer in all return packets.

#### Time to live (TTL)

The number of routing hops the packet may endure. Each time the packet passes through a router/switch, this value is reduced by one. If it ever reaches zero, the packet is discarded. When the board is connected directly to the computer as is a common situation, the TTL is considered almost irrelevant due to the direct link and lack of routing.

#### Protocol

The protocol value is an identifier which specifies what kind of protocol is contained within the packet. For ICMP, UDP and UDP Lite protocols, the value here would be 1, 11 or 88 respectively.

#### IP Header Checksum

Used for error checking.

#### Source Address

The IP address of the sender of the packet

#### **Destination Address**

The IP address of the destination of the packet

#### Data

Contains the network protocol and payload which is being encapsulated by IP.

### 3.2.1 IPv4 vs IPv6

There are two versions of the Internet Protocol in use: IPv4 (Internet Protocol version 4) and IPv6 (Internet Protocol version 6). Version 4 is supported by all networking hardware and software, with version 6 slowly being taken up by various groups such as ISPs as the demand for the newer protocol becomes apparent. However, for the

|      | Bits $0 - 3$        | 4 - 7         | 8 - 11 | 12 - 15 | 16-23       | 24 - 31   |  |

|------|---------------------|---------------|--------|---------|-------------|-----------|--|

| 0    | Version             | Traffic Class |        |         | Flow Label  |           |  |

| 32   | Payload Length      |               |        |         | Next Header | Hop Limit |  |

| 64   | Source Address      |               |        |         |             |           |  |

| 192  | Destination Address |               |        |         |             |           |  |

| 320+ | Data                |               |        |         |             |           |  |

Table 3.3: Structure of the IPv6 header

purposes of this design, the only currently implementation version of the protocol is IPv4 due to the commonality and also the simplicity of implementation. If required however, the core can be enhanced by adding support for IPv6. The changes would involve modifying the first FSM to check the version field of the incoming packet and its value will determine whether to process the packet as a IPv4 or IPv6 packet, and further FSMs can be modified to process IPv6 packets and create new ones in the same manner as other supported protocols. Table 3.3 presents the structure of the IPv6 header.

The various fields of the IPv6 header are:

#### Version

The version of the Internet Protocol. Value of 6 in IPv6.

#### **Traffic Class**

Classifies the packet's priority when there is network congestion.

#### Flow Label

Quality of Service management. Currently unused.

#### Payload Length

The size of the payload in bytes. If this is set to zero, the packet is identified as having a *jumbo payload* with the packet being known as a *jumbogram*.

#### Next Header

Specifies the next encapsulated protocol. This field uses the same values as those specified specified in the IPv4 protocol field.

#### Hop Limit

Replaces the *time to live* field used by IPv4.

#### Source Address

The IP address of the sender of the packet

#### **Destination Address**

The IP address of the destination of the packet

#### Data

Contains the network protocol and payload which is being encapsulated by IP.

## 3.3 ICMP

The Internet Control Message Protocol (ICMP) (RFC 792)<sup>28</sup> is a protocol used to determine the operating status of a network. Used predominately by the *ping* computer program, ICMP packets are sent between machines and can be used to quantify aspects of the quality of the network connection such as latency, robustness, stability and whether a host is reachable. The segment structure of an ICMP packet is presented in Table 3.4 and shows the header information only - actual payload data follows after the header.

|    | Bits 0 - 3 | 4 - 7  | 8 - 15    | 16 - 18 | 19 - 31 |

|----|------------|--------|-----------|---------|---------|

| 0  |            | Sou    | ırce Addı | ess     |         |

| 32 |            | Destir | nation Ac | ldress  |         |

| 64 | Type       |        | Code      | Chec    | ksum    |

| 96 |            | ID     |           | Sequ    | ence    |

Table 3.4: Structure of an ICMP packet

The various fields of an ICMP packet's header are:

## Source Address

The source IP address from whom the packet was sent.

## **Destination Address**

The destination IP address of the packet.

## Type

The ICMP type. Despite there being a fairly large number of available types, only two are used by the ping command and so are supported by the system: 8 (Echo Request, often referred to as just *ping*) and 0 (Echo Reply, also known as a *pong*). When a ping packet is sent by the computer to the board, this is a request for the host to respond so the ICMP packet has a type of 8. When the board replies (assuming the connection is alive), it is replying to the ping which was sent to it, so the responding packet has a type of 0.

## Code

Further specification of the ICMP type. Varies depending on the ICMP type.

## Checksum

This field contains error checking data calculated from the ICMP header and data, with value 0 for this field. This field contains an ID value which should be returned in case of a pong.

## Sequence

This field contains a sequence value which should be returned in case of a pong. Following the sequence, the ICMP payload data is present.

When testing the link between a computer and the FPGA board, a typical use of ICMP is to ping the board to ensure the link is live. Valid replies from the board indicates all aspects of the connection are satisfactory, which includes a correct ARP entry, correct programming of the board and valid interface code on the FPGAs. A more interesting test can involve a *flood ping*, which is when the ping tool is instructed to ping non-stop at the target host the moment it receives a reply, instead of waiting for a pre-determined amount of time before sending another ping. By flooding the host, in this case the FPGA board, a test of stability/reliability can be achieved. A flood ping can be achieved in UNIX-like operating systems with the command (must be run as a super-user): ping  $-f < IP_ADDRESS>$

The protocol is not used for general-purpose data transfer with the exception of the ping tool - its purpose by design is solely to provide information about a network. For this reason it was vital that it be included in the design, particularly for debugging.

# 3.4 ARP

The Address Resolution Protocol (ARP) (RFC 826)<sup>29</sup> is a utility protocol used to translate IP addresses to Ethernet MAC addresses. When a program makes a request to send data to a particular machine, it specifies an IP address as the destination, however the destination network adapter providing the appropriate link does not have

| 32       Hardware length (HLEN)       Protocol length (PLEN)       Operator (OPER)         64       Sender hardware address (SHA)         *       Sender protocol address (SPA)         *       Target hardware address (THA) |    | Bits 0 - 7             | 8 - 15                     | 16 - 31               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------|----------------------------|-----------------------|

| 64       Sender hardware address (SHA)         *       Sender protocol address (SPA)         *       Target hardware address (THA)                                                                                            | 0  | Hardware typ           | be (HTYPE)                 | Protocol type (PTYPE) |

| *       Sender protocol address (SPA)         *       Target hardware address (THA)                                                                                                                                           | 32 | Hardware length (HLEN) | Protocol length (PLEN)     | Operator (OPER)       |

| *     Target hardware address (SPA)                                                                                                                                                                                           | 64 | Sen                    | der hardware address (SH.  | A)                    |

| Iarget hardware address (IIIA)                                                                                                                                                                                                | *  | Sei                    | nder protocol address (SPA | x)                    |

|                                                                                                                                                                                                                               | *  | Tar                    | get hardware address (TH.  | A)                    |

| * Target protocol address (TPA)                                                                                                                                                                                               | *  | Ta                     | rget protocol address (TPA | x)                    |

Table 3.5: Structure of an ARP packet

a native IP address, but rather a MAC address (Media Access Control). Typically, when a request for a particular IP address is made, assuming there are no previous records of the nature of the machines on the link the computer will send an ARP packet requesting a MAC address resolution for the IP address. Any machine on the link which matches the IP address will send a return ARP packet specifying what their MAC address is, so the computer can correctly send the initial request for data transfer to the right machine.

The packet structure of an ARP packet is presented in Table 3.5 (minus the IP header which was covered in Section 3.2).

(Note that the lengths of the SHA, SPA, THA, & TPA fields are determined by the hardware & protocol length fields, so they cannot be explicitly mentioned in the table as they may vary.)

As an example, let's say a host with an IP address of 192.168.0.1 and MAC address of 00:01:02:03:04:05 wants to send a packet to another host at 192.168.0.50, but does not know the MAC address. To determine the MAC address, an ARP request is sent to discover the address. If the host at 192.168.0.50 is running and available then it would receive the ARP request and send the appropriate reply containing its MAC address (which in this example will be 00:40:12:E8:44:A1). This example assumes either a scratch or previously flushed ARP table. The header fields are covered as follows, with the above example being used in the descriptions:

## Hardware type (HTYPE)

Each data link layer protocol is assigned a number used in this field. The system uses Ethernet, which has a value of **1**.

## Protocol type (PTYPE)

Each protocol is assigned a number used in this field. The system uses IPv4, which has a value of 0x0800.

## Hardware length (HLEN)

Length in bytes of a hardware address. Ethernet addresses are 6 bytes long.

## Protocol length (PLEN)

Length in bytes of a logical address. IPv4 addresses are 4 bytes long.

## Operation

Specifies the operation the sender is performing: **1** for a request and **2** for a reply. Hence, the first ARP packet would have a value of **1** and the responding packet would have a value of **2**.

## Sender hardware address (SHA)

Hardware address of the sender

- For the ARP request **0x000102030405** (this the MAC address 00:01:02:03:04:05, represented in HEX and encoded 6 bytes long, as per the hardware length)

- For the ARP reply **0x004012E844A1** (this the MAC address 00:40:12:E8:44:A1, represented in HEX and encoded 6 bytes long, as per the

hardware length. This is the MAC address from the unknown host, which is what the system uses to determine the routing.)

## Sender protocol address (SPA)

Protocol address of the sender

- For the ARP request **0xC0A80001** (this is the IP address 192.168.0.1, represented in HEX and encoded 4 bytes long, as per the protocol length)

- For the ARP reply **0xC0A80032** (this is the IP address 192.168.0.50, represented in HEX and encoded 4 bytes long, as per the protocol length)

## Target hardware address (THA)

Hardware address of the intended receiver

- For the ARP request **0x00000000000** (Since the purpose of the ARP request is to find out this value, ARP request packets have this field set to zero)

- For the ARP reply **0x000102030405** (this the MAC address 00:01:02:03:04:05, represented in HEX and encoded 6 bytes long, as per the hardware length)

## Target protocol address (TPA)

Protocol address of the intended receiver

- For the ARP request **0xC0A80032** (this is the IP address 192.168.0.50, represented in HEX and encoded 4 bytes long, as per the protocol length)

- For the ARP reply **0xC0A80001** (this is the IP address 192.168.0.1, represented in HEX and encoded 4 bytes long, as per the protocol length)

ARP is not particularly difficult to implement, but since FPGA logic needed to satisfy the requirements of both running as fast as possible and retaining the smallest profile so as to allow other programs to access the space on the FPGAs, the decision was made to avoid implementing ARP on the FPGAs by utilising a bypass on the computer. As the system's primary setting will be in a direct connection between the board and a single computer, manually adding an ARP entry on the computer side is easy to do and satisfies the requirements of the system without requiring extra logic. First however, it is necessary to explain how the bypass works.

## 3.4.1 Manual ARP Entries

Operating systems keep track of the various MAC addresses and their corresponding IP addresses through the use of an *address translation table*. These tables are used by the operating system to work out where a packet should go, since packets only specify the destination in the form of an IP address and not as a MAC address. When a new IP address is used for the first time, the OS does not have any knowledge about the relevant MAC address it refers to, so the OS sends an ARP request to all machines on the IP's subnet and waits for a reply from the appropriate machine. Once it receives the ARP reply, the translation table is updated to make note of the IP-to-MAC relationship and so all future uses of that particular IP will been seen in the table and automatically use the relevant MAC address without requiring a second use of ARP. If an ARP request is made and no machine responds with a relevant ARP reply within the timeout period, the requested IP is not written into the table as there are no available hosts.<sup>30</sup>

This system does not currently support ARP, which means that when connected directly to a computer, the computer will know a link has been established (because the physical components on the board achieve this independently of the VHDL code), but the computer will not be able to understand what's at the other end because ARP requests will go unnoticed. This means that any attempts to ping the board or send UDP transmissions will fail because every attempt will automatically be preceded by an ARP request. The operating system will only stop sending ARP requests and allow regular network traffic once it has an entry for the board in the address translation table and since the board does not achieve this on its own, we must perform the addition of the entry ourselves.

Adding an entry to the ARP table is performed using the *arp* command available on most operating systems.<sup>31</sup> For example, in both Windows and Linux an ARP entry can be manually set using the following command: **arp** -s <IP\_ADDRESS> <MAC\_ADDRESS>

The IP\_ADDRESS (which can also be a hostname) is the address we want the board to be known as and the MAC address is the physical address of the board. Unlike most other networked devices, the board does not have a hardwired MAC address to begin with, so the MAC address specified can be virtually anything, so long as it doesn't match any other network devices already connected to the computer. The other requirement is to pick an IP address that exists on the subnet of the network adapter's IP address, the adaptor which connects to the board. For example, if the network adaptor has an IP address of 192.168.0.1 and the subnet mask is 255.255.255.0, then an IP address of 192.168.0.50 is valid for the board since it exists within the allocated subnet. After executing the arp command with valid arguments, the board is then accessible using the chosen IP and can be validated with using the standard ping command. A full example of how to use the arp command along with the other necessary steps involved to connect the board to a computer is covered in Section 7.2.

Setting the ARP for the FPGA board manually allows access to the board with a specified IP without having to implement ARP construction/deconstruction code in

the FPGA. This increases available space for other programs on the FPGA and also makes the routing easier for the interface, ensuring an easier chance of matching full gigabit speeds. The main disadvantage is that in more complicated networking situations, if the board is not directly connected to the end of the networking jack of a computer but somewhere down a chain of networked devices, such as on a router/switch, the board will not be understood by the devices it's directly connected to unless that device itself has an ARP entry added for the board. This may or may not even be possible, particularly if connected to a router/switch that doesn't support manual addition of ARP entries. The implementation of ARP construction/deconstruction on the FPGA can be considered a future improvement to the design, but can still be worked around provided the networking requirements are simple.

# 3.5 TCP

The Transmission Control Protocol (TCP) (RFC 793)<sup>32</sup> is a data transfer protocol, considered one of the core protocols of the Internet protocol suite. It provides reliable delivery of packets and acts as the major backbone of most Internet communications, such as with file transfer, email and web browsing. The segment structure of a TCP packet is shown in Table 3.6 (contains header and data information - IP header is not included in the diagram as it was covered in Section 3.2):

The fields are summarised as follows:

Source port

Identifies the sending port

#### **Destination port**

Identifies the receiving port

|           | Bits 0 - 3  | 4 - 7     | 8 - 15   | 16 - 31          |

|-----------|-------------|-----------|----------|------------------|

| 0         | So          | urce port |          | Destination port |

| 32        |             | Sequen    | ce numbe | er               |

| 64        |             | Acknowled | gment nu | mber             |

| 96        | Data offset | Reserved  | Flags    | Windows          |

| 128       | Check       | sum       | Ur       | gent pointer     |

| 160       |             | Options   | (optiona | al)              |

| 160/192 + |             | - I       | Data –   |                  |

Table 3.6: Structure of a TCP packet

## Sequence number

The sequence number designates the position of the current packet's first data byte in the data stream. If the SYN flag is present, the sequence number is the position plus one, to allow for the SYN flag in the payload. For example, if the first data byte of the current packet is the 100th byte in the data stream so far, the sequence number will be 100 if the SYN flag is absent, or 101 if the SYN flag is present.

## Acknowledgment number

If the ACK flag is present, then the value of this field is the sequence number that the sender of the acknowledgment expects next.

## Data offset

Specifies the size of the TCP header in 32-bit words. The minimum size header is 5 words and the maximum is 15 words thus giving the minimum size of 20 bytes and maximum of 60 bytes. This field gets its name from the fact that it is also the offset from the start of the TCP packet to the data.

## Reserved

For future use and should be set to zero

## Flags (aka Control bits)

Contains 8 bit flags

- ECE (ECN-Echo) indicate that the TCP peer is ECN capable during 3-way handshake

- URG indicates that the URGent pointer field is significant

- ACK indicates that the ACKnowledgment field is significant

- PSH Push function

- RST Reset the connection

- SYN Synchronise sequence numbers

- FIN No more data from sender

## Window

The number of data bytes which the sender of this segment is willing to accept, beginning with the byte indicated in the acknowledgment field.

## Checksum

The 16-bit checksum field is used for error-checking of the header and data

## Urgent pointer

If the URG flag is set, then this 16-bit field is an offset from the sequence number indicating the last urgent data byte

## Options

The total length of the option field must be a multiple of a 32-bit word and the data offset field adjusted appropriately

Despite TCP being a significant component of the Internet Protocol, it is not implemented at all in this design. There are several reasons for this:

- 1. TCP is a complex protocol. This complexity translates into extra logic required on the FPGA, which limits the potential speeds and room for extra programs on the FPGA. Justification for such implementation would only work if there were no realistic alternatives.

- 2. UDP (covered below) is a simpler protocol which has similar properties to TCP but without much of the reliability architecture. However, reliability can be effectively added to UDP without much overhead, so this negates the issue of using UDP in preference to TCP.

- 3. TCP requires extra overhead to cover the error-correction/reliability it provides. As can be seen in the header diagram, a lot of the header fields exist just for this protection, which makes it less efficient than the UDP standard which uses far less header per packet. Since the intention of the design is to supply a highspeed, high-bandwidth device, removal of overheads such as this are desirable.

- 4. The extra reliability of the packet transmission provided by TCP is just not necessary for this design. For the purposes of this core there was no intention to have it embedded within devices connected to the Internet; it is mostly intended for local networks and/or direct connection to a computer. Ultimately the extra effort to implement TCP would not be justified compared to that of UDP.

TCP was originally designed for unreliable low-speed networks. However, as network speeds have increased the hardware requirements for the network adaptors to support TCP have had to increase as well. If an embedded CPU on an FPGA intended to process TCP packets, Gigabit networking may result in issues with the CPU keeping up with the line speed. As a general rule of thumb, 1 MHz of CPU is required for every 1 Mbits of TCP traffic, so if the CPU was solely responsible for processing TCP packets and their payloads, a Gigabit link would require at least a 1 GHz CPU to keep up with the line speed.<sup>33</sup> Embedded processors on FPGAs generally aren't able to run at such speeds; for example, the popular MicroBlaze soft processor core for Xilinx FPGAs has a maximum clock frequency of 115 MHZ on a Spartan 3, and even on a Vertex 5 the maximum possible speed is only 235 MHz.<sup>34</sup> This has been the reason for development in TCP offload engines which transfer processing of the TCP stack to the network controller logic instead of solely on a CPU. In many commercial applications however, TCP is rarely coded entirely in hardware; for the situations where a device requires the use of TCP, a common strategy is to provide a combination solution, by way of an embedded CPU to run the state machines in software using code and perform the checksum calculations in hardware using logic.<sup>35</sup> This provides a more efficient and balanced implementation than by using just logic. An example of such an implementation is used by Treck Inc. and their embedded Internet protocol stacks.<sup>6</sup>

# 3.6 UDP

The User Datagram Protocol (UDP) (RFC 768)<sup>36</sup> provides the bulk of the data transfer capability for the project. It is connectionless, which means no handshaking is required between the two devices. This along with several other features means the protocol is simple to implement in hardware, but does not guarantee reliability or ordering in the way TCP does. The segment structure of a UDP packet is shown in Table 3.7; note that it contains header and data information - IP header is not included in the diagram as it was covered in Section 3.2.

36

Table 3.7: Structure of a UDP packet

|    | Bits 0 - 15 | 16 - 31          |

|----|-------------|------------------|

| 0  | Source port | Destination port |

| 32 | Length      | Checksum         |

| 64 |             | Data             |

The UDP header consists of four fields:

## Source port

This field identifies the sending port. When a packet is sent by the computer this port is generally assigned a random number. Any packets sent by the board back to the computer utilise this port number for the packet's destination port.

## **Destination port**

This field identifies the destination port.

## Length

A 16-bit field that specifies the length in bytes of the entire datagram: header and data. The minimum length is 8 bytes since that's the length of the header. The field size sets a theoretical limit of 65, 527 bytes for the data carried by a single UDP datagram. The practical limit for the data length which is imposed by the underlying IPv4 protocol is 65, 507 bytes.

#### Checksum

The 16-bit checksum field is used for error-checking of the header and data. Implementing the UDP Checksum is optional, as the standard allows for the UDP checksum field to be zeroed out to denote no checksum and hence for devices to ignore the checksum entirely. However, it is still fully implemented in the design for two main reasons:

| 0Source address32Destination address64ZeroesProtocolUDP length96Source PortDestination Port128LengthChecksum160Data |     | Bits 0 - 7 | 8 - 15      | 16 - 23  | 24 - 31  |

|---------------------------------------------------------------------------------------------------------------------|-----|------------|-------------|----------|----------|

| 64ZeroesProtocolUDP length96Source PortDestination Port128LengthChecksum                                            | 0   |            | Source a    | ddress   |          |

| 96Source PortDestination Port128LengthChecksum                                                                      | 32  | I          | Destination | address  |          |

| 128LengthChecksum                                                                                                   | 64  | Zeroes     | Protocol    | UDP      | length   |

|                                                                                                                     | 96  | Source     | Port        | Destinat | ion Port |

| Data                                                                                                                | 128 | Leng       | th          | Chec     | ksum     |

|                                                                                                                     | 160 |            | Data        | a        |          |

Table 3.8: Structure of the UDP pseudo-header with remaining UDP packet

- Although the zeroed-checksum UDP packets will pass through to the computer unhindered, any programs which utilise the Berkley socket interface for communication will not accept the packets unless they have a filled in (and valid) UDP checksum. As this constitutes the majority of the system's communication strategy, UDP checksums must be implemented fully to allow for sockets to be used.

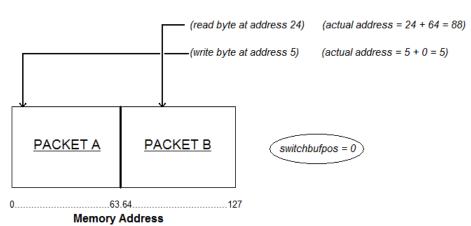

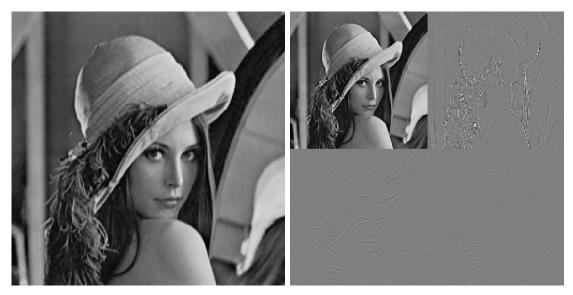

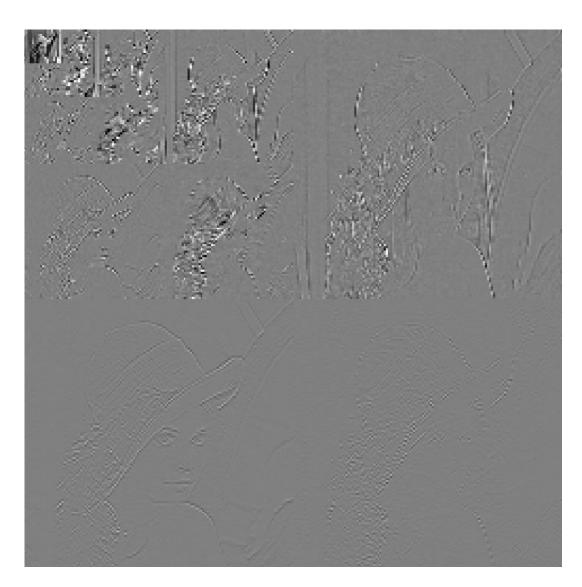

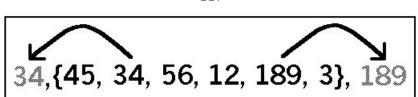

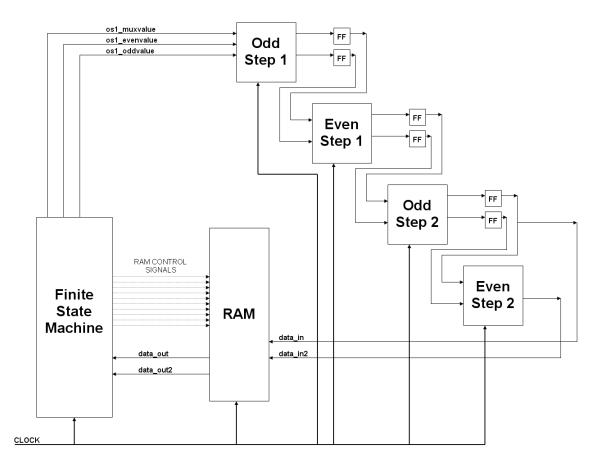

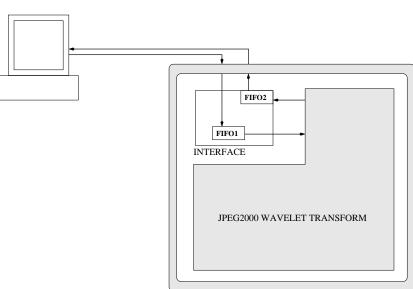

- 2. UDP has less inbuilt error-correction capabilities than TCP, so enabling UDP checksums ensures the received packets are uncorrupted and provide at least some form of protection from unintentionally accepting corrupted packets.